SoCs for critical applications could use 28% less energy and 48% less chip area while offering hardware failure rate nine times lower, if they were designed using the Desyre architecture, according to the European project. The result, the project adds, would reduce hospital costs and replacement rate of medical devices drastically.

SoCs for critical applications could use 28% less energy and 48% less chip area while offering hardware failure rate nine times lower, if they were designed using the Desyre architecture, according to the European project. The result, the project adds, would reduce hospital costs and replacement rate of medical devices drastically.

The DeSyRe (on-Demand System Reliability) project was established to examine the development of extremely reliable medical devices. It initially promised new design techniques that would counter the increasing fault rates expected for SoCs manufactured on next technology nodes.

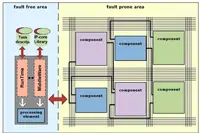

Desyre's approach sees an SoC split into two parts. One part accommodates interchangeable processing cores which, the project says, are fault prone by nature. The other part is fault resistant and monitors the 'sanity' of cores in the first area. According to the project, it assures that each core in that area can handle an assigned task correctly and efficiently, transferring tasks to idle cores in case of a malfunction.

"We have coupled a new dynamically reconfigurable substrate together with runtime-system software support in such a manner that it can adapt on demand to various types and densities of faults, system constraints and application requirements," said Ioannis Sourdis, Associate Professor in Computer Engineering at Chalmers University of Technology and leader of the Desyre project. "We compared the Desyre architecture to prevailing reliability approaches and Desyre scored better on all aspects. It even scored better than we planned at the start of the project."

When compared to a standard Triple Modular Redundancy (TMR) system, an SoC developed using the Desyre approach required 46% less chip area and 28% less energy to achieve the same tolerance to transient faults and the same performance as a typical TMR system. When compared to a time redundant system, Desyre SoCs were said to execute code between 14% and 32% more quickly.

When looking at permanent faults and comparing the Desyre system with a core redundant system of the same area, Desyre reduced the number of failures in a billion device hours (FIT) by a factor of nine.

"We expected that Desyre would reduce the FIT by about 40% at most, and were very pleased to reach a reduction in the number of failures by more than a factor of nine," asserts Riccardo Mariani, CTO of project partner Yogitech. "The Desyre techniques were created for extremely reliable medical SoCs, but their use is not limited to that market. I expect Desyre like systems to be in our future cars – for instance in self driving cars – as we design automotive SoCs with ever more fail safe and fail operational measures to meet the strict functional safety standards."

Author

Graham Pitcher

Source: www.newelectronics.co.uk