В цифровых многоканальных системах дистанционного пропорционального управления моделями [1-3] сигналы, содержащие информацию об угловом положении исполнительного органа сервоприводов, формируются изменением ширины канальных импульсов, вырабатываемых шифратором передатчика. Их длительность, в зависимости от положения рукояток управления передатчика, может изменяться в интервале 1...2 мс. Для передачи информации по каналу связи эти импульсы преобразуются в импульсы фиксированной длительности 0,1...0,5 мс, образующие канальные посылки, которые разделены синхропаузой и следуют с частотой 50...60 Гц. Информация о передаваемом значении в соответствующем канале управления содержится во временном интервале между импульсами канальной посылки, а число импульсов в ней зависит от числа каналов управления. Дешифратор приёмника распределяет импульсы этой последовательности по каналам, восстанавливает ширину канальных импульсов и передаёт их на соответствующие сервоприводы.

В этих системах дистанционного управления моделями при воздействии различного рода помех не исключено появление на входе дешифратора приёмника посторонних импульсов, вызывающих переключение его счётчика наряду с импульсами канальной посылки, формируемыми шифратором передатчика, что приводит к появлению на выходе дешифратора ложных команд управления и, как следствие, аварии модели.

Один из способов борьбы с этими помехами заключается в селекции импульсов канальной посылки по длительности: на вход дешифратора приёмника пропускаются только те импульсы, длительность которых находится в интервале, соответствующем длительности импульсов канальной посылки своего передатчика [1].

Как правило, большинство электронных устройств, реализующих на практике этот способ борьбы с помехами, - аналоговые. Они преобразуют длительность импульсов канальной посылки в напряжение, сравнивают его с заданными пороговыми уровнями и по результату этого сравнения формируют управляющий сигнал, разрешающий или запрещающий прохождение соответствующего импульса канальной посылки на вход дешифратора. Недостатки этих устройств - относительно низкая стабильность работы и сложность налаживания.

Предлагаю свободный от указанных недостатков свой вариант селектора-формирователя импульсов заданной длительности.

Основные технические характеристики

Длительность селектируемых импульсов, мс .......0,3±0,08

Номинальная длительность формируемых импульсов, мс .........................0,3

Напряжение питания, В..........5...9

Потребляемый ток, мА, не более ........................15

По уровню входных и выходных сигналов селектор-формирователь импульсов совместим с КМОП-микросхемами.

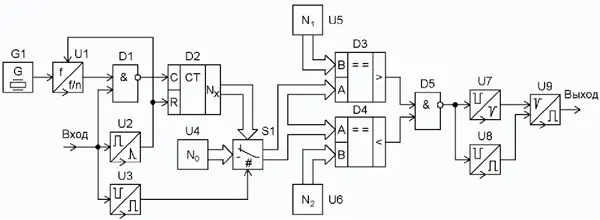

Функциональная схема селектора-формирователя импульсов заданной длительности представлена на рис. 1. Он включает в себя логические элементы 2И-НЕ D1, D5; двоичный счётчик импульсов D2; цифровые компараторы D3, D4; генератор прямоугольных импульсов G1; многоканальный электронный переключатель S1; делитель частоты U1; формирователи коротких импульсов U2, U7; инвертирующие элементы U3, U8; формирователи цифровых кодов U4-U6; одновибратор U9.

Рис. 1. Функциональная схема селектора-формирователя импульсов заданной длительности

Селектор-формирователь импульсов заданной длительности (далее по тексту - селектор) работает так. Генератор G1 вырабатывает на своём выходе последовательность прямоугольных импульсов частотой f, которую понижает делитель частоты U1 в n раз, где n - целое число больше единицы, и поступает на первый вход логического элемента 2И-НЕ D1, второй вход которого соединён с входом селектора.

В момент появления на входе селектора импульса канальной посылки высокого логического уровня длительностью Δt на выходе формирователя коротких импульсов U2 возникает короткий импульс высокого логического уровня, который, воздействуя на вход R двоичного счётчика D2 и аналогичный вход делителя частоты U1, устанавливает эти функциональные узлы в нулевое состояние. Инвертирующий элемент U3 при наличии на входе селектора высокого логического уровня формирует на своём выходе низкий логический уровень, который, воздействуя на управляющий вход многоканального электронного переключателя S1, подключает к входам A цифровых компараторов D3, D4 выходы формирователя цифрового кода U4, формирующего на них двоичное число N0.

Двоичные числа N1, N2, формируемые на выходах формирователей цифровых кодов U5, U6, подключённых к входам B цифровых компараторов D3, D4 соответственно, и число N0 соотносятся между собой так: N0 < N1 < N2. Поэтому в момент подключения входов A цифровых компараторов D3, D4 к выходам формирователя цифрового кода U4 на выходе A > B компаратора D3 формируется низкий логический уровень, а на выходе A < B компаратора D4 - высокий уровень. Следствие этого - появление на выходе логического элемента 2И-НЕ D5 напряжения высокого уровня, а на выходе инвертирующего элемента U8 - низкого уровня. Напряжение низкого логического уровня, подаваемое с выхода инвертирующего элемента U8 на вход разрешения одновибратора U9, блокирует его работу, при этом на выходе одновибратора U9 присутствует напряжение низкого уровня.

При поступлении на второй вход логического элемента 2И-НЕ D1 импульса канальной посылки высокого логического уровня длительностью Δt на тактовый вход C двоичного счётчика D2 с выхода делителя частоты U1 проходят прямоугольные импульсы напряжения частотой f/n. Двоичный счётчик D2 в течение времени Δt подсчитывает их число. По истечении времени At на втором входе логического элемента 2И-НЕ D1 появляется низкий логический уровень, в результате чего на выходе этого элемента формируется высокий уровень. Счёт импульсов счётчиком D2 прекращается, и на его выходах фиксируется двоичное число Nx, равное числу импульсов, поступивших на его тактовый вход C за время Δt.

По истечении времени At на выходе инвертирующего элемента U3 формируется высокий уровень, который поступает на вход управления многоканального электронного переключателя S1, при этом к входам A цифровых компараторов D3, D4 подключаются выходы двоичного счётчика D2 и отключаются от входов A этих компараторов выходы формирователя цифрового кода U4.

Нижняя и верхняя границы интервала длительности импульсов канальной посылки, разрешённых к прохождению на выход селектора, заданы двоичными числами N1 и N2 соответственно. Если длительность импульса Δt канальной посылки на входе селектора находится в пределах границ разрешённого интервала, т. е. выполняется условие N1 < Nx < N2, то в момент подключения к входам A цифровых компараторов D3, D4 выходов двоичного счётчика D2 на выходе A > B и A < B соответствующего компаратора появляется высокий логический уровень, вследствие чего в этот момент на выходе логического элемента 2И-НЕ D5 формируется импульсный перепад с высокого на низкий логический уровень. В результате этого на выходе инвертирующего элемента U8 формируется высокий логический уровень, который разрешает работу одновибратора U9, а формирователь коротких импульсов U7 формирует на своём выходе перепад с высокого на низкий логический уровень и обратно, запускающий одновибратор U9. В результате этого в момент окончания действия импульса канальной посылки на входе селектора на его выходе формируется прямоугольный импульс напряжения фиксированной длительности.

Если длительность импульса Δt канальной посылки на входе селектора не превышает нижнюю границу разрешённого интервала, т. е. выполняется условие N1 > Nx < N2, то в момент подключения к входам A цифровых компараторов D3, D4 выходов двоичного счётчика D2 на выходе A > B цифрового компаратора D3 формируется низкий логический уровень, а на выходе A < B цифрового компаратора D4 - высокий уровень. Следствием этого является формирование высокого логического уровня на выходе логического элемента 2И-НЕ D5 и низкого логического уровня на выходе инвертирующего элемента U8, соответственно на входе разрешения одно-вибратора U9. В этом состоянии одновибратор U9 заблокирован, а на выходе селектора формируется низкий логический уровень.

Если длительность импульса Δt канальной посылки на входе селектора превышает верхнюю границу разрешённого интервала, т. е. выполняется условие N1 < Nx > N2, то в момент подключения к входам A цифровых компараторов D3, D4 выходов двоичного счётчика D2 на выходе A > B цифрового компаратора D3 формируется высокий логический уровень, а на выходе A < B цифрового компаратора D4 - низкий уровень, следствием чего является формирование напряжения высокого уровня на выходе логического элемента 2И-НЕ DD5, при этом аналогично предыдущему случаю на выходе селектора формируется низкий логический уровень.

Таким образом, на выходе селектора появляются импульсы фиксированной длительности только в том случае, если длительность импульсов канальной посылки на его входе находится в заданных пределах, соответствующих длительности импульсов канальной посылки своего передатчика.

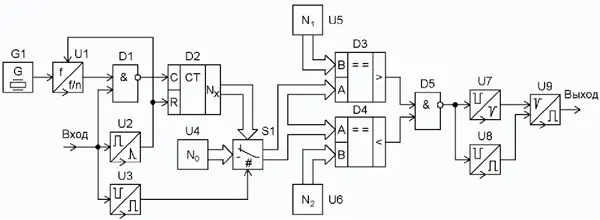

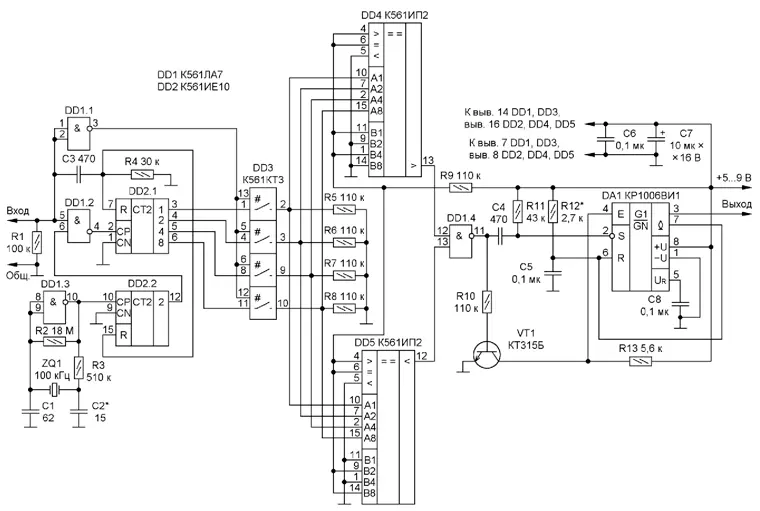

Принципиальная схема селектора представлена на рис. 2. Микросхемы DD1-DD5 в соответствии с рис. 1 выполняют следующие функции: DD1.1 - инвертирующий элемент U3; DD1.2 - логический элемент 2И-НЕD1; DD1.3 - активный элемент генератора прямоугольных импульсов напряжения G1, включающего в себя резисторы R2, R3, конденсаторы C1, C2 и кварцевый резонатор ZQ1; DD1.4 - логический элемент 2И-НЕ D5; DD2.1 - двоичный счётчик импульсов D2; DD2.2 - делитель частоты на четыре U1; DD3 - четырёхканальный электронный переключатель S1; DD4, DD5 - цифровые компараторы D3, D4.

Рис. 2. Принципиальная схема селектора

Резисторы R5-R8 образуют формирователь цифрового кода U4. При размыкании ключей микросхемы DD3 эти резисторы отключаются от соответствующих выходов двоичного счётчика DD2.1, в результате чего на выводах резисторов R5-R8, соединённых с входами A1, A2, A4, A8 цифровых компараторов DD4, DD5, формируется двоичное четырёхразрядное число N0 = 00002 (010). При замыкании ключей микросхемы DD3 резисторы R5-R8 становятся нагрузочными для соответствующих выходов двоичного счётчика DD2.1, формирующего двоичное четырёхразрядное число Nx, подаваемое на входы A1, A2, A4, A8 цифровых компараторов DD4, DD5.

Резистор R9 и совокупность электрических связей, устанавливающих на соответствующих входах B1, B2, B4, B8 цифровых компараторов DD4, DD5 низкие и высокие логические уровни, образуют формирователи цифровых кодов U5, U6, при этом N1 = 01012 (510), а N2 = 10102 (1010).

Дифференцирующие цепи R4C3 и R11C4 - формирователи коротких импульсов напряжения U2 и U7 соответственно. Транзистор VT1, резисторы R10, R13 - инвертирующий элемент U8. На микросхеме DA1, интегрирующей цепи R12C5 и конденсаторе C8 собран одно-вибратор U9. Длительность его выходного прямоугольного импульса - 0,3 мс.

Резистор R1 служит для устранения неопределённого состояния логического элемента 2И-НЕ DD1.2 при отсутствии подключения входа селектора к источнику сигнала. Конденсаторы C6, C7 - фильтрующие в цепи питания.

Монтаж селектора выполнен навесным способом на макетной плате. Конденсатор C5 - плёночный К73-17, его можно заменить конденсаторами К73-9, К73-24. Оксидные и керамические конденсаторы - импортные, вместо них можно использовать отечественные К50-35 и К10-17-1а соответственно. Постоянные резисторы - С2-33, возможная замена - С2-23, МЛТ, ОМЛТ Транзистор КТ315Б допустимо заменить другим этой же серии или подобным других серий. Микросхемы серии К561 могут быть заменены функциональными аналогами серии 564 или импортными. Интегральный таймер КР1006ВИ1 заменим импортным серии 555.

Проверку функционирования селектора производят так. К его входу подключают генератор регулируемых по длительности прямоугольных импульсов, амплитуда которых соответствует логическим уровням КМОП-микросхем, а к выходу - осциллограф. Устанавливают частоту выходного сигнала этого генератора равной 50 Гц и, изменяя длительность его выходных импульсов, убеждаются в появлении на выходе селектора прямоугольных импульсов длительностью 0,3 мс только в том случае, если длительность импульсов на входе селектора не менее 0,22 мс и не более 0,38 мс. При необходимости длительность выходных импульсов селектора корректируют подборкой резистора R12.

Литература

1. Войцеховский Я. Дистанционное управление моделями. Пособие моделиста и радиолюбителя. Пер с польск. Под ред. А. П. Павлова и Н. Н. Путятина. - М.: Связь, 1977, с. 180-186, 188-195.

2. Миль Г. Электронное дистанционное управление моделями. Пер. с нем. В. Н. Палья-нова. - М.: ДОСААФ, 1980, с. 45-114.

3. Днищенко В. А. 500 схем для радиолюбителей. Дистанционное управление моделями. - СПб.: Наука и техника, 2007, с. 20- 37, 64-121, 352-355.

Автор: О. Ильин, г. Казань