Общие сведения

ИМС STi5500 OMEGA, анонсирована фирмой STMicroelectronics в октябре 1997 года. Она стала первым законченным многофункциональным декодером для цифровых ресиверов и абонентских терминалов, предназначенных для приёма программ стандартов DVB-C, DVB-S и DVB-T. Высокая интеграция функциональных узлов декодера позволила производителю приёмного оборудования цифрового ТВ максимально снизить конечную стоимость устройств, минимизировав затраты на компоненты. Наличие мощного МК позволило при проектировании устройств создавать удобный пользовательский интерфейс.

В октябре 1998 года фирма анонсирует ИМС STi5505, предназначенную для применения в DVD-проигрывателях. ИМС являлась усечённым вариантом STi5500 - у нее отсутствовал TS0 демультиплексор, а также DES- и DVB-дескремблеры. Дальнейшее описание архитектуры и функциональных возможностей ИМС будет приводиться на основе ИМС STi5500.

Архитектура и функциональное описание

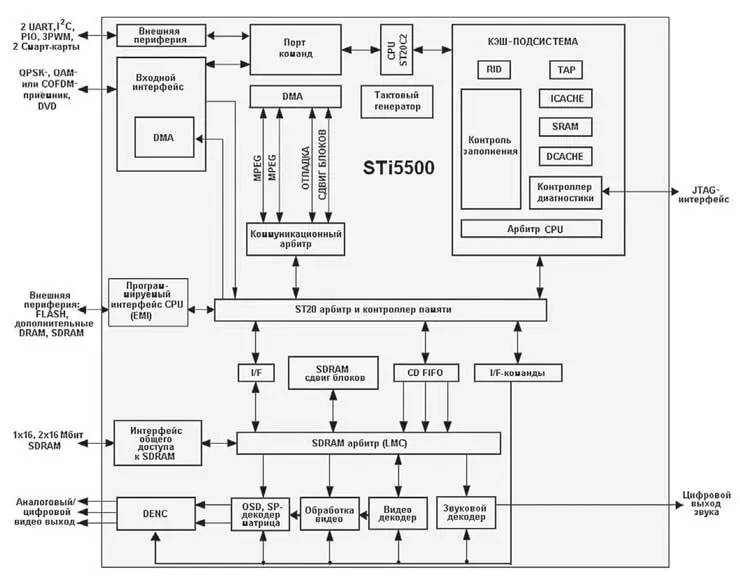

ИМС STi 5500 входит в семейство однокристальных декодеров STi55xx. Её блок-схема показана на рис. 1. Как все ИМС входящие в семейство OMEGA, STi5500 имеет на своём кристалле TS-демультиплексор, декодер MPEG-2 видео- и аудиосигналов, 32-битный МК семейства ST20, генератор OSD-графики, цифровой DENC-видеокодер, расширенную периферию. В схему также включена система защиты от нелегального копирования MACROVISION™7.01/6.1. Наличие в составе транспортного демультиплексора секторного процессора и дешифратора CSS-криптов позволяет использовать ИМС для поддержки DVD-совместимых устройств.

Рис. 1. Функциональная блок-схема ИМС STi5500

ИМС STi5500 - программируемый декодер сигналов TS-потока стандарта MPEG-2, разработанный с учётом технических требований стандартов DVB и DSS. Функции демультиплексора отрабатываются в модуле с помощью аппаратных средств. Этот блок может быть сконфигурирован для обработки потока битов для двух указанных стандартов, включая DES- и DVB-дескремблирование, а также выделение SI-информации.

1. Процессорное ядро, внутренняя шина и внешние соединительные интерфейсы

В основе CPU STi5500 лежит 32-х битное процессорное ядро ST20-C2, работающее на тактовой частоте 50 МГц. Оно содержит логику исполнения команд, указатели команд/данных и регистры операндов. Ядро непосредственно получает доступ к высокоскоростной статической памяти SRAM на кристалле, которая может хранить программу или данные.

Процессорное ядро ST20-C2 позволяет выполнять следующие функции под управлением ПО:

- запуск драйверов устройства и синхронизация их работы;

- распределение ресурсов системы;

- функцию электронного навигатора программы EPG;

- поддержку модулей условного доступа CI.

Для уменьшения времени доступа к внешним программам и памяти данных используется внутренняя кэш-память. Процессор может получить доступ к внешней памяти через EMI-интерфейс общего назначения или через EMI SDRAM-интерфейс, который используется совместно с MPEG-2-декодером.

Система памяти SRAM на кристалле обеспечивает внутреннюю полосу пропускания данных до 200 Мбайт/с, поддерживая конвейерный внутренний доступ к памяти за 2 цикла длительностью 20 нс. Система памяти состоит из 2 кбайт SRAM, 2 кбайт кэша команд и 2 кбайт кэша данных (последний может быть сконфигурирован как SRAM) и внешнего интерфейса памяти EMI.

У ИМС STi5500 имеется на кристалле памяти 2 кбайт SRAM, преимущество которой заключается в способности сохранить ограниченный по времени исполнения код программы внутрикристально, например, прервать исполнение программы, ПО ядра или драйверов устройств и часто используемые данные без их удаления из кэша.

Кэш команд и кэш данных являются непосредственно адресуемыми, есть система отложенной записи для кэша данных. Кэш поддерживает пакетный доступ к внешней памяти для заполнения и отложенной записи, который наиболее эффективен для увеличения эффективности работы в страничном режиме с памятью SDRAM.

Интерфейс EMI управляет доступом к внешней памяти и периферии, в то время как интерфейс EMI SDRAM обеспечивает совместный доступ к буферу SDRAM для декодера MPEG, МК ST20 и DMA-периферии. Интерфейс EMI может получить доступ к 16 Мбайт (или более - при использовании DRAM) физического адресного пространства в каждом из четырех банков памяти общего назначения, и обеспечивает поддержку скорости передачи до 80 Мбайт/с.

Интерфейс EMI SDRAM имеет полосу пропускания до 200 Мбайт/с, внутренние соединения памяти STi5500 обеспечивают буферирование, и арбитраж доступа к памяти и позволяют получить очень высокую пропускную способность при доступе к памяти.

Система прерываний STi5500 имеет восемь приоритетных уровней и три входа от внешних источников прерывания. Логика назначения уровня позволяет любому из внутренних или внешних прерываний быть при необходимости на любом уровне прерывания.

Системный сервисный модуль STi5500 включает в себя следующие узлы:

- генератор тактовых частот с петлёй ФАПЧ (PLL), тактируемый внешним сигналом частотой 27 МГц и формирующий все внутренние тактовые частоты для синхронизации различных узлов декодера;

- стандартный IEEE 1149.1 порт TAP, совместимый с JTAG-интерфейсом;

- диагностическое контрольное устройство DCU.

Устройство DCU обеспечивает через интерфейс JTAG следующие функции:

- настройку во время разработки устройства;

- аппаратные точки останова и точки просмотра;

- оперативную трассировку в реальном времени;

- поддержку внешней фиксации логического состояния LSA.

Доступный через DCU код CPU ID для ИМС STi5500-0xD4C9041, а для ИМС STi5505-0xD4CB041.

2. Входной интерфейс связи

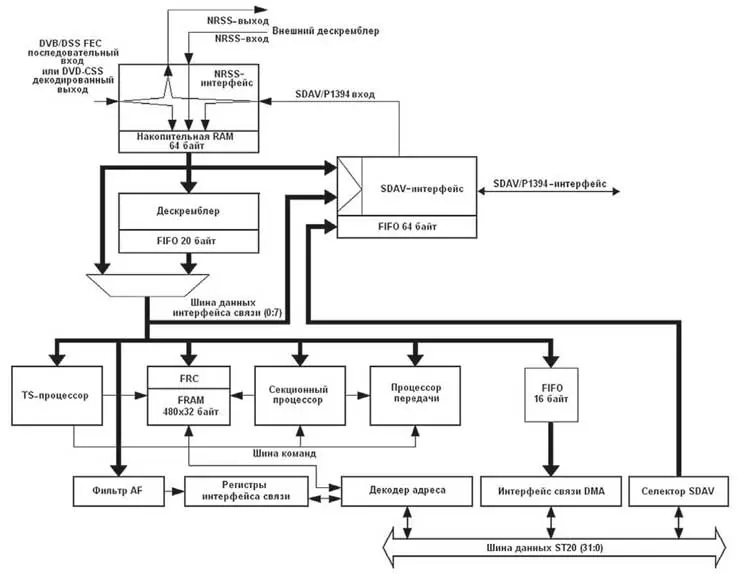

На вход аппаратного TS-демультиплексора ИМС STi5500 поступает TS-поток систем DVB или DSS, а также поток программы DVD (рис.2). TS-демультиплексор извлекает из потока (возможно, скремблированного), сжатые байты данных последовательности пакетов элементарных потоков PES (Packetized Elementary Stream), принадлежащих одной выбранной пользователем программе, которая будет декодирована и представлена на выходе ИМС.

Рис. 2. Функциональная блок-схема входного интерфейса связи ИМС STi5500

Кроме того, байты сервисных данных секционных потоков извлекаются из потока битов и сохраняются в соответствующих буферах, которые будут использоваться блоком управления декодера. Высокая скорость передачи данных цифрового интерфейса позволяет обеспечить передачу TS-пакетов между ресивером и внешними устройствами для их записи или воспроизведения. Данный интерфейс SDAV (Simplified Digital Audio Video) оказывает полную поддержку внешней cвязиIEEE1394.

Защищённый интерфейс NRSS (National Renewable Security System) также включен в TS-демультиплексор для обеспечения внешнего интерфейса в системах DVB, DSS или пакетов DVD. Во входном интерфейсе связи определены два уровня:

- уровень пакетов PES или секций для информации PSI (Program Specific Information);

- уровень пакетов TP (Transport Packets).

Демультиплексор TS-потока выполняет полную обработку на уровнях TP, пакетов PES или секций.

Он используется для подачи на MPEG-2 декодер и центральный процессор поступающий поток данных. Демультиплексор состоит из следующих узлов:

- накопительная память RAM (AR) и NRSS-интерфейс;

- дескремблер случайных последовательностей (DESCR);

- интерфейс SDAV-1394;

- RAM фильтра-селектора (FRAM); блок процессора (TS процессор, процессор секции, процессор передачи);

- фильтр-селектор области адаптации;

- узел восстановления тактовых импульсов;

- вычислитель DMA.

Сигналы во входном интерфейсе и системные тактовые импульсы TS-демультиплексора асинхронны. Байты TP, получаемые с помощью последовательно/параллельного конвертера, буферизируются в AR, которая представляет собой стек FIFO. Обработка пакета должна быть начата, прежде чем будет установлен программируемый уровень AR, и, по крайней мере, на её входе полные данные.

Для дескремблирования доступны системы кодирования как DVB, так и DES. Поддерживается декодирование на уровнях DVB, TP и PES. Для стандарта DSS скремблирование производится только на уровне TP. При этом может быть применено до 8 различных наборов ключей для дескремблирования до 32 потоков, которые хранятся в памяти FRAM. Они автоматически загружаются после PID-фильтрации.

Если полезные данные в принятых TP скремблированы, дескремблер случайных последовательностей настроен так, чтобы обеспечить обращение к дескремблеру и получить от него декодированные байты. Если полезные данные не скремблиро-ваны, байты полезных данных посылаются в обход дескремблера.

Высокоскоростной двунаправленный цифровой интерфейс используется для того, чтобы передать TP между ресивером и внешними устройствами. Шина SDAV - двухточечное соединение. Она позволяет иметь всего один источник на любом шинном сегменте одновременно. Поскольку входная тактовая частота равна 40 МГц и скорость передачи данных по шине SDAV - 49,1 Мбит/с, требуется буферизация для предотвращения опустошения данных в интерфейсе.

Стандарт IEEE 1394 представляет одиночный интерфейс ввода-вывода с простым соединителем, который может обращаться к множеству устройств через единственный порт. Это позволяет обеспечить одновременную передачу на скоростях передачи данных до 400 Мбит/с. Из-за сложности стандарта IEEE 1394 и существенных в то время затрат на его реализацию STi5500 был оснащён одиночным интерфейсом SDAV, который оказывал полную поддержку для внешнего интерфейса IEEE 1394. Этот блок получает поступающий поток пакетов и переформатирует его для шины SDAV/1394. Он также берет поступающую информацию с шины SDAV/1394 и восстанавливает соответствующий поток пакетов.

Блок фильтрации PID содержит фильтр-селектор для получения TP пакетов только одной программы. Он извлекает транспортные пакеты (до 32 потоков) из поступающего потока битов.

Вторая функция фильтра применяется ко всем данным для получения информации о типе секции. Для каждого потока может быть до 32 целей, с которыми может быть сравнен поступающий заголовок секции. Максимальная длина целей составляет 16 байтов для DSS и 14 байтов для DVB. Каждая часть каждой цели может быть замаскирована индивидуально. Для одного целевого байта необходимы два байта RAM. Общее количество целевых байтов определено размером множества используемого RAM фильтра.

Фильтрация области адаптации выполнена для того, чтобы извлечь информацию PCR или отказаться от любых нежелательных данных, содержавшихся в извлеченном TP-пакете.

3. Декодер MPEG-2, компоновщик и DENC-кодер

Видеодекодер MPEG-2 обрабатывает в реальном времени сигналы стандартов MPEG-1 и MPEG-2 с разрешающей способностью 720 х 480 х 60 Гц и 720 х 576 х 50 Гц. Для преобразования форматов изображения декодер осуществляет горизонтальную и вертикальную фильтрацию сигналов.

Видеодекодер декодирует полное изображение и затем останавливается, пока не поступит команда на декодирование следующего изображения, приходящего в потоке битов видеоизображения. Обычно расшифровка нового изображения начинается в ответ на запуск отображения нового изображения. Регистры, содержание которых может измениться от изображения к изображению, дублированы и обновляются автоматически, когда начинается декодирование. Поток битов считывается из битового буфера в декодер кодов переменной длины VLD (Variable-Length code Decoder) и начинается реконструкция изображения. Любые предсказатели требуют быть перенесенными из соответствующей области внешней памяти, а восстановленное изображение записывается в область памяти, предназначенную для декодированного изображения.

В то время как декодируется изображение, селектор кода начала используется для того, чтобы определить местонахождение начала следующего заголовка изображения, который читает центральный процессор, чтобы настроить дублированные регистры для декодирования следующего изображения. Все эти задачи могут быть синхронизированы, используя прерывания, генерируемые на стартовых кодах и вертикальных синхронизирующих сигналах.

Пользовательские меню могут быть отображены на экране посредством OSD-графики. Отображаемая информация выводится на экран с помощью компоновщика трёх уровней. Первый уровень - уровень декодированного MPEG-изображения, на который накладываются уровни субизображения и OSD-графики.

Внутренний цифровой кодер DENC преобразует мультиплексированный YCbCr-поток 4:2:2 или 4:4:4 в стандартный аналоговый ПЦТС стандартов PAL или NTSC. На выходе также можно получить компонентные сигналы RGB, YUV или YC. Сигналы телетекста, приходящие в MPEG-пакетах данных, запоминаются в буфере и по требованию могут быть подмешаны в выходной аналоговый сигнал в стандарте CCIR/ITU-R Broadcast Teletext System B (WST). Кодер поддерживает систему защиты от нелегального копирования Macrovision™.

4. Звуковой декодер (звуковая подсистема)

Звуковой декодер обрабатывает следующие стандарты: MPEG-1 (Audio Layers I и II, MPEG-2 Audio Layer II, PCM. Он получает поток битов сжатых данных из звукового буфера, который расположен во внешней памяти SDRAM. Когда используется внешний интерфейс AC-3, компрессированные или PCM-данные также приходят от звукового буфера. Звуковой буфер - память, расположенная в ад ресном пространстве регистров/сжатых данных таким же образом, как и буферы декодеров изображений. Данные передаются, используя передачу сжатых данных с помощью DMA-вычислителя или центрального процессора.

Звуковой декодер полностью автономен, он не нуждается во взаимодействии с ПО во время декодирования, кроме таких ситуаций, как возникновение состояния ошибки и приём вспомогательных данных в звуковом потоке.

Выходной сигнал декодера - цифровой многоканальный, совместно с тактирующим сигналом он может подаваться на внешний ЦАП, преобразующий звук в аналоговую форму. Декодированные звуковые данные выводятся в последовательном формате PCM (в форматах I2S или SONY.)

По звуковому интерфейсу передаются следующие сигналы:

- PCMDATA - последовательный вывод данных PCM;

- SCLK - выход тактовых импульсов PCM;

- LRCLK - выход выбора левого/правого каналов;

- PCMCLK - вход тактовых импульсов PCM.

5. Периферийные устройства

ИМС STi5500 имеет на кристалле широкий набор последовательных интерфейсов, обеспечивающих синхронную и асинхронную связи с внешними устройствами. Это два асинхронных последовательных интерфейса ASC (Asynchronous Serial Controller) или UART. Два из них обычно используются как контроллеры доступа к смарт-картам (по протоколу ISO7816-3). Интерфейсы ASC поддерживают различные режимы передачи, генерацию бита чётности, программирование количества битов остановки передачи.

Синхронную последовательную связь обеспечивает контроллер SSC (Synchronous Serial Controllers) - высокоскоростной интерфейс для обмена информацией с внешней памятью, микроконтроллерами или приёмниками дистанционного оборудования. Интерфейс SSC поддерживает протоколы SPI (Serial Periferal Interface) и I2C. Его также можно запрограммировать для работы с другими стандартами синхронной передачи данных.

Модуль ШИМ и счётчика содержит три ШИМ модулятора, три ШИМ декодера (входы захвата) и четыре программируемых таймера. Каждый вход захвата может быть сконфигурирован на детектирование фронта или спада импульса, фронта и спада одновременно и отсутствие перепадов (состояние выключено). Синхронизация модуляции и захвата осуществляется двумя независимыми сигналами.

Параллельные 34-битные порты I/O сконфигурированы в четыре порта, каждый бит которых может быть сконфигурирован как на ввод, так и на вывод. Большинство линий портов имеют альтернативные функции и могут выступать связными линиями для выполнения функций ASC, SSC и т.д.

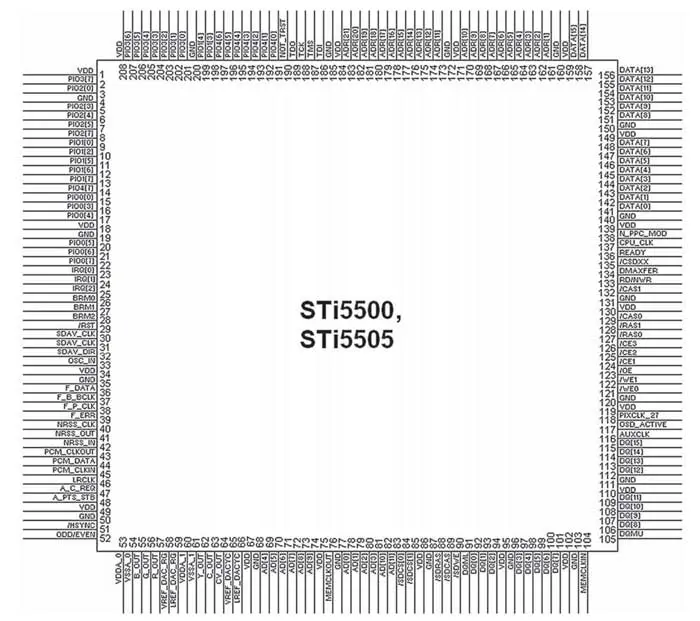

Конфигурация выводов и исполнение корпуса

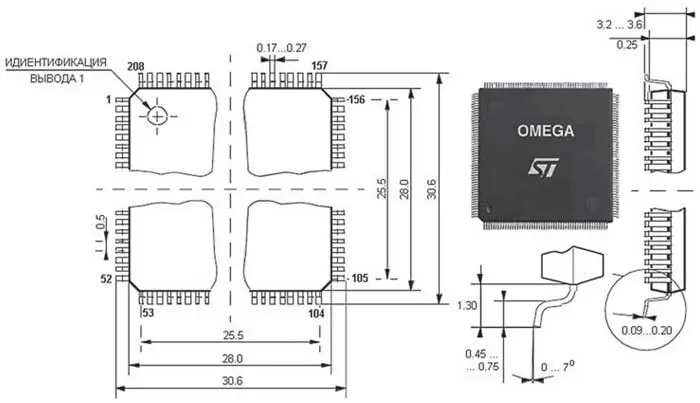

ИМС STi5500 STi5505 (рис. 3) выпускались в 208-выводном пластмассовом корпусе PQFP (Plastic Quad Flat Pack), показанном на рис. 4. ИМС питается от одного источника питания +3,3 В.

Рис. 3. Расположение и назначение выводов ИМС STi5500, STi5505

Рис. 4. Корпус PQFP208

Ниже приводятся примеры, связанные с выходом из строя ИМС STi5505, требующих их замену, на примере DVD проигрывателя JBL DVD600.

Типичные неисправности, связанные с выходом из строя ИМС

При включении проигрывателя в сеть сетевой индикатор не светится. Напряжения на выходе блока питания отсутствуют

При отключении блока питания от основной платы напряжения на нём появляются, что говорит о его исправности. Проверяют омметром сопротивления между линией питания ИМС IC201 STi5505AVB +3,3 В и корпусом. Сопротивление оказалось менее 10 Ом (т.е. в цепи было короткое замыкание). Была демонтирована IC201, короткое замыкание в цепи при этом пропало. После замены IC201 работоспособность устройства восстановилась.

При подключении проигрывателя к сети включается рабочий режим. Сервоуправление работает, изображение отсутствует

Композитный и компонентные видеосигналы на выв. 62-64 STi5505AVB отсутствуют. Проверка сопротивления между этими выводами и корпусом проигрывателя показала короткое замыкание. Замена ИМС восстановила работоспособность проигрывателя.

Данные дефекты возникают при неправильной эксплуатации СТВ приёмников и DVD-проигрывателей, в основном, при неправильном подсоединении к проигрывателю ТВ приёмника.

Ресиверы и DVD-проигрыватели, выполненные на ИМС STi5500 и STi5505

На основе ИМС STi5500 и STi5505 в своё время были спроектированы и стали очень популярны устройства следующих марок:

1. СТВ ресиверы (DVB-S, STi5500): "BOTECH 2001 CI", "DSR 2000 FTA", "ELSTAR ZDX9111E", "NEXTWAVE DX300", "PBI DVR-1000S", "PHONOTREND SDR-2600", "SKYMASTER DX10 CI", "TELEVES RDS 7235".

2. DVD-проигрыватели (STi5505): "HARMAN/KARDON DVD1", "HARMAN/KARDON DVD10", "PHILIPS DVD960", "SEG DVD 1000", "VESTEL DVD 2100", "YAMAHA DVD-S520".

Источник: Ремонт и сервис