В серии LH2000 фирмы LG Electronics представлены 19-42" ЖК телевизоры с минималистским дизайном и специальной системой энергосбережения, значительно снижающей расход электроэнергии. Автор подробно описывает схемотехнику шасси и сервисные регулировки.

Основные характеристики и возможности телевизоров

Основные характеристики и возможности телевизоров приведены в таблице 1.

Таблица 1. Основные характеристики телевизоров LG серии LH2000

Характеристика | Описание |

Тип ЖК панели | TFT LCD HD с диагоналями 19"/22"/26"/32"/37"/42" |

Формат экрана | 16:9 |

Задняя подсветка | От 2 до 16 (в зависимости от диагонали панели) люминесцентных ламп с холодным катодом CCFL (Cold Cathode Fluoresced Lamp) |

Системы цветности аналогового вещания | PAL, SECAM, NTSC |

Стандарты цифрового вещания | DVB-T/C MPEG-4 |

Телетекст | С памятью на 1000 страниц |

Стереозвук | Поддержка системы NICAM |

Выходная мощность каналов звука | 2x3 Вт |

Наличие технологии Clear Voice | Да |

Яркость | Не менее 500 Кд/м2 |

Динамическая контрастность | Не хуже 50000:1 |

Максимальное разрешение | 1366x768 |

Угол обзора | Не менее 178° |

Интерфейсные входы-выходы | Коаксиальный антенный вход, компонентный видеовход (X CB/PB, CR/PR) и аудиовходы (L, R), входы SCARTx2, вход RGB для персонального компьютера (ПК), VGA для ПК при использовании телевизора в качестве монитора, HDMI/DVI, USB (сервисный порт), RS-232C (сервисный порт), Ethernet (RJ-45), аудио от ПК или цифрового телевизора (DTV), оптический выход цифрового звука, разъем для головных телефонов |

Наличие слота CI/PCMCIA | Да |

Наличие таймера сна и защиты от детей | Да |

Потребляемая от питающей сети мощность | Не более 40 Вт |

Напряжение и частота питающей сети | 100...240 В, 50/60 Гц |

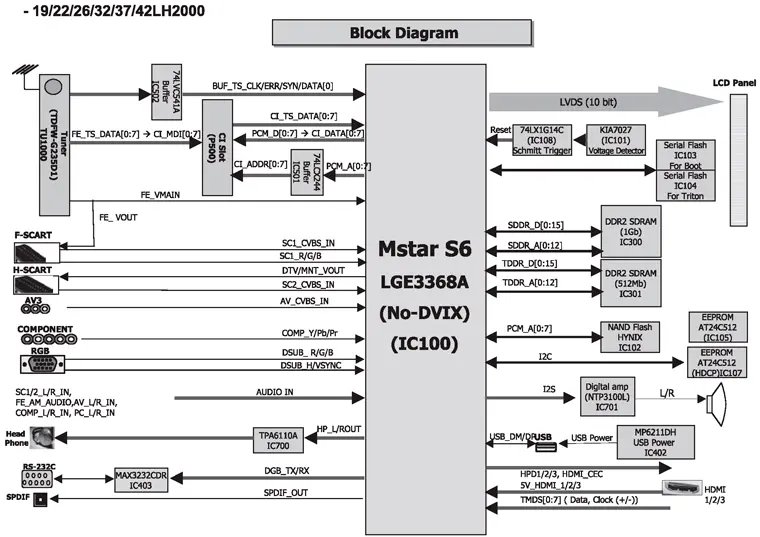

Структурная схема

Телевизоры LG серии LH2000 выполнены на шасси LD91A/G. В состав этого шасси входят следующие узлы и блоки:

1. Основная плата (Main Block), на которой размещены:

- центральный процессор IC100;

- тюнер TU1000 (в некоторых моделях он имеет позиционное обозначение TU1200);

- микросхемы ЭСППЗУ (EEP-ROM) IC105 и IC107;

- микросхемы ОЗУ (SDRAM) IC300 и IC301;

- буферные микросхемы IC501 и IC502;

- усилители мощности звуковых сигналов для головных телефонов (IC700) и динамиков (IC701);

- микросхема управляемой (Hand) Flash-памяти IC102;

- микросхемы Flash-памяти загрузки (Boot) IC103 и программирования (Triton) IC104;

- схема сброса на микросхемах IC101 (детектор напряжения) и IC108 (триггер Шмитта);

- интерфейсы внешних устройств (IC400, IC402, IC403);

- формирователи и стабилизаторы питающих напряжений;

- узел подключения внешних разъемов SCART;

- буферный усилитель звуковых сигналов для SCART IC1103;

- узел соединений (MODULE&CTL);

- мультимедийный интерфейс HDMI на микросхемах IC600-IC602;

- интерфейс карт памяти CI/PCMCIA на микросхемах IC500-IC502 (совпадает с позиционными обозначениями буферных микросхем);

2. Блок (плата) питания и инверторов PCB;

3. Плата клавиатуры управления;

4. Плата фотоприемника и индикаторов;

5. LCD-панель с конструктивно объединенной с ней платой масштабирования (Scaler);

6. Звуковые динамические головки (по одной или по две в каждом канале).

Структурная схема основной платы приведена на рис. 1.

Рис. 1. Структурная схема основной платы

Рассматриваемое ТВ-шасси реализовано на основе процессора IC100 типа LGE3368A (Saturn6 No-DivX). При приеме аналогового радиосигнала с тюнера TU1000 на процессор поступают аналоговые видеосигнал FE_VMAIN и сигнал звука FE_AM_AUDIO (последний после обработки сигнала ПЧ звука SIF).

В случае приема цифрового радиосигнала с тюнера снимается цифровой 8-битовый аудио/видео поток MPEG-2/MPEG-4 FE_TS_DATA[0:7] и через контакты разъема Р500 подключения слота карт памяти CI/PCMCIA подается на процессор (новое обозначение CI_TS_ DATA[0:7]). Одновременно через буфер на микросхеме IC502 на процессор подается цифровой синхросигнал BUF_TS_CLK/ERR/SYN/DATA[0].

Обмен информацией со слотом карт памяти производится за счет сигналов PCM_D[0:7]>CI_DATA[0:7] и PCM_A[0:7] (последний после буфера на микросхеме IC501 имеет обозначение CI_ADDR[0:7]).

При приеме аналогового радиосигнала видеосигнал FE_VOUT с тюнера поступает также на разъем F-SCART. С этого разъема на процессор IC100 могут быть поданы внешние видеосигналы SC1_CVBS_IN SC1_R/G/B.

С разъема Н-SCART на процессор IC100 может быть подан видеосигнал SC2_CVBS_IN, а с процессора через этот разъем поступают видеосигналы на другой телевизор или монитор DTV_MNT_VOUT.

С одного из трех гнезд разъема AV3 на процессор может быть подан видеосигнал AV_CVBS_IN.

Компонентный видеосигнал COMP_Y/ PB/PR может быть подан на процессор с разъемов RCA (COMPONENT).

Через контакты разъема RGB с ПК на процессор могут быть поданы сигналы основных цветов DSUB_R/G/B и синхросигналы DSUB_H/VSYNC.

С указанных выше разъемов на процессор могут быть поданы также соответствующие звуковые сигналы SC1/2_L/R_IN, AV_L/R_IN, COMP_L/R_IN и PC_L/R_IN.

На телефонное гнездо Head Phone с процессора через усилитель на микросхеме IC700 поступает звуковой сигнал HP_L/ROUT.

Цифровая информация DGB_TX/RX с процессора через преобразователь уровней IC403 поступает на контакты сервисного разъема последовательного интерфейса RS-232C, предназначенного для сервисного обслуживания ТВ.

На разъем оптического выхода цифрового канала звука SPDIF с процессора IC100 поступает звуковой сигнал SPDIF_OUT.

Процессор и ЖК панель связаны между собой интерфейсом LVDS. С выхода этого интерфейса на ЖК панель подается 10-битный цифровой сигнал изображения.

Сигнал начального сброса Reset подается на процессор от детектора напряжения на микросхеме IC101 через триггер Шмитта на микросхеме IC108.

Процессор имеет двунаправленные интерфейсы с запоминающими устройствами:

- с последовательной Flash-памятью загрузки (Boot) на микросхеме IC103 и Flash-памятью программ (Triton) на микросхеме IC104;

- с динамической памятью SDRAM на микросхеме IC300 - сигналы SDDR_D[0:15] и SDDR_A[0:12];

- с динамической памятью SDRAM на микросхеме IC301 - сигналы ТDDR_D[0:15] и ТDDR_A[0:12];

- с управляемой Flash-памятью (HYNIX) на микросхеме IC102, служащей для хранения данных ПК, - сигнал PCM_A[0:7];

- с устройствами EEPROM на микросхемах IC105 и IC107 - через цифровую шину I2C.

По цифровой шине I2S процессор управляет цифровым усилителем сигналов звука на микросхеме IC701, к стереофоническим выходам которого L/R подключены динамические головки телевизора.

Сигналы детектирования "горячего" подключения цифровых мультимедийных устройств HDMI_ HDP_1/2/3 и сигналы двунаправленной цифровой шины дистанционного управления HDMI_CEC снимаются с процессора IC100 и подаются на соответствующий контакт розетки входного порта HDMI/DVI. Напряжение питания 5V_HDMI_1/2/3 и мультиплексированный во времени сигнал синхронизации видеосигнала TMDS[0:7] (Data, Clock) с ее соответствующих контактов подаются на процессор и другие узлы основного блока.

Принципиальная электрическая схема

Принципиальная электрическая схема ТВ-шасси LD91A/G приведена в архиве (см. ниже).

В телевизорах применен универсальный тюнер TU1000 (в некоторых моделях он имеет позиционное обозначение TU1200) типа TDFW-G235D, фактически содержащий в своем составе два тюнера - цифровой 0X1E и аналоговый 0X86. Схема подключения тюнера в составе основной платы приведена в архиве.

Активация того или другого тюнера и управление ими производится процессором IC100 по цифровой шине FE_TUNER_SCL, FE_TUNER_SDA (выв. 11, 10 TU1000). Информация о работе тюнера передается в процессор по цифровой шине FE_DEMOD_SCL, FE_DEMOD_SDA (выв. 19, 18 соответственно).

При работе аналогового тюнера с его выв.15 на процессор IC100 через буферный каскад на транзисторе Q1205 подается ПЦТС FE_VMAIN, а с выв. 17 через буферный усилитель на транзисторе Q1201 - сигнал ПЧ звука FE_SIF. На выв. 6 тюнера с процессора подается сигнал АРУ RF_AGC (в некоторых опциях не непосредственно, а через каскад на транзисторе Q1200).

С выв. 24-34 цифрового тюнера на процессор поступает цифровой поток MPEG-2/MPEG-4 по следующим шинам: FE_TS_CLK, FE_TS_DATA[7] - FE_TS_DATA[0], FE_TS_VAL, FE_TS_SYN.

Для проверки кодов цифрового потока на устройство проверки, выполненное на микросхеме IC1201 типа NL17SZ08DFT2G, поступают сигналы FE_TS_VAL и FE_TS_ERR с выв. 33 и 23 тюнера соответственно. В случае какого-либо нарушения с выхода микросхемы на процессор поступает сигнал FE_TS_VAL_ERR, который используется для коррекции работы тюнера.

На цифровой тюнер с процессора через двухкаскадный усилитель на транзисторах Q1202 и Q1203 также подаются сигналы начального сброса FE_RESET (на выв. 20) и сигнал загрузки FE_BOOSTER_CTL (на выв. 2).

Питание тюнера осуществляется:

- через выв. 4, напряжение +5 В(+B[5V]) поступает от источника +5V_GENERAL;

- через выв. 21, напряжение +3,3 В (3.3V) поступает от источника +3.3V_TUNER;

- через выв. 22, напряжение + 1,2 В (1.2V) поступает от источника + 1.2V_TUNER.

В архиве (см. ниже) размещены принципиальные схемы включения процессора IC100 основной платы и связи его выводов с другими узлами этой платы.

Процессор IC100 связан цифровой шиной (EEPROM_SCL, EEP-ROM_SDA) с EEPROM на микросхеме IC105 типа M24512-WMW6 и с EEPROM HDCP (протокол защиты широкополосных цифровых данных) на микросхеме IC107 типа САТ24WC08W-T Выводы линий этой шины в процессоре: F8, D11.

По линиям цифровой шины SPI_CK, SPI_DI процессор связан с последовательной Flash-памятью загрузки на микросхеме IC103 типа W25X32VSSIG (выводы процессора AD11, AE11). Для совместной работы телевизора с ПК процессор связан по цифровой шине PCM_A[0:7] с микросхемой Flash-памяти IC102 типа HY27US08121B-TPCB (выводы процессора AB16, AC15, AC14, AB14, AC12, AB8, AC13, AA9).

Сигнал начального сброса высокого уровня (примерно 2,7 В) формируется микросхемой IC101 типа KIA7427F(или KIA7027F) и подается на выв. D4 процессора. Для контроля порогового напряжения питания служит устройство детектирования на микросхеме IC1500 типа KIA7042AF, выходное напряжение с которого POWER_DET (примерно 4,2 В) поступает на выв. Н6 процессора.

На этот же вывод поступает контрольный сигнал с процессора обработки изображений ISP_TXO.

Аналоговый видеосигнал FE_VMAIN с выв. 15 тюнера (см. рис. 3) поступает на выв. W1 процессора IC100.

Сигнал ПЧ звука FE_SIF подается на выв. W3 процессора IC100. Видеосигналы с внешних разъемов SC1_CVBS, SC2_CVBS, AV_CVBS подаются на выв. U3, U2, T1 процессора. Соответствующие сигналы звука с внешних разъемов SC1_L_IN, SC1_R_IN, SC2_L_IN, SC2_R_IN, AV_L_IN, AV_R_IN подаются на выв. V1, AA5, AE2, AE3, AB1, AA1 процессора соответственно.

Для связи с устройствами, подключенными через интерфейс DVI, используются следующие выводы процессора: P1, P2, G2, G3, H3, Q1, H1, H2, A1, B2, A2, C3, B1, C1, C2, D2, D3, E3, D1, E1, F3, E2, AE8, AD8, AD2, AF8, AF9, AE9, AE10, AC10, AE7, AF7, AD7, J9.

С контактов разъема SCART_RGB сигналы могут быть поданы на выв. N2, N1, P2, P3, R1, R2 процессора, с контактов разъема DSUB - на выв. K3, K2, L1, L3, K1 процессора, а с контактов разъема COMP - на выв. V1, V2, U1 процессора.

Дифференциальные сигналы интерфейса LVDS (в составе процессора IC100) LVA_(0-4)P, LVA_(0-4)M, LVA_CKP, LVA_CKM, LVB_(0-4)P, LVB_(0-4)M, LVB_CKP, LVB_CKM подаются на ЖК панель со следующих выводов процессора: AE16, AD16, AD15, AF16, AF15, AE15, AD13, AF14, AF13, AE13, AE14, AD14, AE20, AD20, AD19, AF20, AF19, AE19, AD17, AF18, AF17, AE18, AD18.

Сигналы звука AUDIO_MAS-TER_CLK, MS_L/R_CK, MS_L/R_CH, MS_SCK подаются на выходные усилители с выв. A3, B7, C7, D8 процессора.

Напряжения питания подаются на следующие выводы процессора:

- 1,26 В ( + 1.26V_VDDC), на выв. D18, D17, D16, D19, D20, H18, H19, H20, J20, K20, L20, M20, P7, R7, T7, T22, V7, V22, W11, W12, W19, W20, W22, V22;

- 3,3 В (+3.3V_VDDP), на выв. H9, H10, H11, H12, N20, P20, W9, W10;

- 3,3 В (+3.3V_AVDD_AU), на выв. W7;

- 3,3 В (+3.3V_AVDD_MEMPL), на выв. H17, T20, V20, H7;

- 3,3 В (+3.3V_AVDD_LPLL), на выв. R20;

- 3,3 В (+3.3V_AVDD_33) - на выв. J7, K7, L7, M7, N7;

- 3,3 В (+3.3V_AVDD_DM) - на выв. W5;

- 3,3 В (+3.3V_AVDD_OTG) - на выв. H8.

ОЗУ на микросхемахIC300 и IC301 связаны цифровыми шинами SDDR_D[0:15], SDDR_A[0:12] и TDDR_D[0:15], TDDR_D[0:12] с центральным процессором IC100. Эти связи показаны на схемах в архиве.

Микросхема SDRAM IC300 типа HY5PS1G1631CFP-S6 объемом 1 Гбайт подключена по линиям адресной шины к выв. C13, A22, B13, C22, A13, A23, C12, B23, B12, C23, B22, A12, A24 процессора, а по линиям шины данных - к выв. B15, A21, A15, B21, C21, C14, C20, C15, C18, C19, B18, B20, A20, A16, B19, A17.

Микросхема SDRAM IC301 типа H5PS5162FFR-S6C объемом 512 Mбайт подключена по линиям адресной шины к выв. T28, AF26, T25, AF23, T24, AE23, R28, AD22, R25, AC22, AD23, R24, AE22 процессора, а по линиям шины данных - к выв. W25, AE26, W24, AF24, AF25, V26, AE25, W26, V28, AD26, V25, AE24, AD26, V24, AD24, AA24.

Обмен сигналами управления и контроля между микросхемой IC300 и процессором осуществляется через выв. C24, B24, D24, B14, A14, D23, D14, D13, D12, D22, B18, C17, C18, A19, A18, B17 последнего. Обмен между микросхемой IC301 и процессором происходит через его выв. AC23, AC24, AB22, V25, V24, AB23, U26, U25, U24, AB24, AB26, AA26, AC25, AC26, AB25, AA25.

Эта часть схемы питается напряжением 1,8 В от источника + 1.8V_DDR, которое подается на следующие выводы:

- D15 процессораIC100;

- J2, A1, E1, J9, M9, R1, A9, C1, C3, C7, C9, E9, G1, G3, G7, G9, J1 микросхемы IC300;

- J2, J1, A1, E1, J9, M9, R1, A9, C1, C3, C7, C9, E9, G1, G3, G7, G9 микросхемы IC301.

Используемое ОЗУ позволяет запоминать полный кадр видеосигнала, что, в свою очередь, дает возможность его преобразования:

- изменение стандарта или формата (частота кадров "50 Гц" и "100 Гц", масштаб 4:3 и 16:9, прогрессивная развертка и чересстрочная и др.);

- режимы "Кадр в кадре" (PIP), "Стоп-кадр" и др.;

- включение узлов медианной фильтрации изображения и т.п.

Микросхема IC701 типа EAN60664001 служит для обработки и усиления звуковых сигналов, поступающих в цифровой форме с центрального процессора. Входной сигнал звука подается с процессора по линиям цифровой шины MS_LRCH, MS_LRCN, MS_SCN на выв. 17, 18, 19 микросхемы. Усиленные стереосигналы SPK_L+, SPK_L- и SPK_R+, SPK_R- снимаются с выв. 54, 53, 48, 47 и 37, 36, 31, 30 микросхемы и подаются на динамические головки SPEAK-ER_L и SPEAKER_ R. Каждый из этих выходных стереосигналов зеркально симметричен относительно общего провода, поэтому в схеме нет необходимости иметь габаритные разделительные конденсаторы большой емкости.

Микросхема IC701 управляется процессором по линиям шины SCL_SUB/AMP, SDA_SUB/AMP.

Сигналы блокировки (отключения) звука SB_MUTE, NTP_MUTE подаются на выв. 25 микросхемы от процессора через каскад на буферном транзисторе Q701.

Сигнал начальной установки (сброса) AMP_RST подается на выв. 3 микросхемы IC701, тактовый сигнал (синхронизирующий) AUDIO_MASTER_CLK - на ее выв. 7.

Питающие напряжения AMP_VCC и +1.8V_AMP подаются на выв. 50, 51,12,13,16 микросхемы.

Звуковые сигналы головных телефонов HP_LOUT, HP_ROUT с выхода усилителя IC700 типа TPA6110A2DGNRG4 подаются на контакты разъемов наушников JK700 и JK701. Сигналы блокировки (отключения) звука в наушниках SB_MUTE, SIDE_HP_MUTE подаются через буферные каскады на транзисторах Q705, Q700 на выв. 3 микросхемы IC700

В архиве приведены схемы интерфейсов, расположенных на основной плате:

- внешних сигналов AV (OPT: SIDE_AV) (опция - устанавливается не во всех моделях);

- компонентных сигналов (COMPONENT) яркости COMP_Y цветности COMP_PB и COMP_PR и звука COMP_L_IN и COMP_R_IN;

- сигналов звука от ПК или другого цифрового телевизора(PC AUDIO);

- оптических цифровых выходных сигналов звука (SPDIF OPTIC JACK) для их подачи на другие цифровые устройства по оптическому кабелю (цифровой оптический интерфейс фирм SONY и PHILIPS);

- видеосигналов RGB от ПК;

- сервисных сигналов регулировки с помощью ПК через интерфейс RS-232C;

- сигналов регулировки и сервисного обслуживания через разъем USB. В опции REAR_USB он размещен на задней стенке телевизора, а в опции SIDE_USB - с боковой стороны.

В схеме интерфейса входных видеосигналов RGB от ПК используется микросхема ЭСППЗУ IC400 типа САТ24C02W1-GT3, а в схеме интерфейса входного последовательного порта RS-232C - микросхема драйвера/приемника IC403 типа MAX3232CDR.

На основной плате расположены также стабилизаторы и преобразователи, формирующие необходимые напряжения питания других узлов телевизора (см. архив).

Через контакт 1 разъема Р801 подается напряжение 24/15 В (+24V/+15V) с платы питания и инверторов РСВ. Указанный разъем используется в моделях с диагональю экрана 19"/22".

В моделях с большим экраном напряжение 24/15 В подается через контакты разъема Р800.

Из напряжения +24/+15 В с помощью стабилизатора на транзисторе Q807 формируются напряжения 12/15 В (+12V/+15V) и отдельно 12 В ( + 12V). Стабилизатор выключается/включается с помощью ключа на транзисторе Q803, на базу которого подается сигнал POWER_ON/OFF1.

Из напряжения 12/15 В стабилизатором на транзисторе Q806 формируется напряжение питания ЖК панели PANEL_POWER. Для этого используется стабилизатор на транзисторе Q806. Ключ Q804 Q805, управляемый сигналом PANEL_CTL, служит для включения и выключения напряжения питания панели.

С помощью синхронного понижающего преобразователя напряжения на микросхеме IC808 типа MР2305DS из напряжений 12 В формируется базовое напряжение 5 В (+5V_GENERAL) и напряжения 5 В (+5V_USB_REAR и +5V_USB_SIDE), предназначенные для питания устройств интерфейса USB. В некоторых моделях телевизоров как опция используется ключ на транзисторах Q808, Q809. С его помощью для питания устройств USB и ЖК панели сигналом POWER_ON/OFF1 можно подавать напряжение дежурного режима 5 В (+5V_ST) при отсутствии напряжения 12 В.

Из напряжения +5V_GENERAL стабилизатором IC809 типа AP1117E33G-13 формируется напряжение +3.3V_TUNER, предназначенное для питания тюнера.

Из напряжения +5V_ST стабилизатором IC801типа AP1117E33G-13 формируется напряжение дежурного режима +3.3V_ST.

Из напряжения +5V_ST с помощью понижающего конвертора IC806 типа MР2212DN формируются стабилизированные напряжения +3.3V и +1.26V_VDCC, последним питается ядро центрального процессора.

Из напряжения +3.3V, в свою очередь, формируются напряжение питания усилителя +1.8V_AMP (стабилизатор IC803 типа AP1117E18G-13) и питания тюнера + 1.2V_TUN (стабилизатор IC804 типа AZ1117K-1.2TRE1).

И, наконец, с помощью понижающего конвертора со встроенным мощным полевым транзистором IC806 типа BD9150MUV из напряжения +5V_ST формируются напряжения +3.3V_AVDD и +3.3V_CI, питающие центральный процессор и устройство CI/PCMCIA соответственно.

Имеющийся на основной плате соединительный узел MODULE&CTL (см. архив) содержит следующие разъемы для подключения ЖК панели: Р1301 (для удобства подключения через него ЖК панели он выполнен в виде пластины), Р1302 (для 26" моделей), Р1306 (для 19"/22" моделей). В качестве опции для 19"/22" моделей применяется разъем Р1300.

Для формирования изображения с центрального процессора на ЖК панель через контакты разъема Р1301 подаются следующие дифференциальные сигналы: LVDS LVA_(0-4)P, LVA_(0-4)M, LVA_CKP, LVA_CKM, LVB_(0-4)P, LVB_(0-4)M, LVB_CKP, LVB_CKM.

Через контакты этого же разъема по линиям цифровой шины управления MENC_SCL 1:L21, MENC_SDA 1:L21 подаются управляющие сигналы, а также сигналы начального сброса MENC_RESET.

Напряжение питания PANEL_POWER подается на ЖК панель через контакты 1-4 разъема Р1301, контакты 27-30 разъема Р1302, контакты 1-3 разъема Р1306 и контакты 1-5 разъема Р1300.

Через контакты 45 разъема Р1301 и 22 разъема Р1302 поступает сигнал выбора режима HD/FHD, через контакт 25 разъема Р1301 - сигнал выбора разрядности 8BIT/10BIT, а через контакты 42 разъема Р1301 и 21 разъема Р1302 - сигнал разрешения/запрета включения панели.

Соединительный узел имеет также разъемы Р1303, Р1304, Р1305, через контакты которых по цепям KEY1, KEY2 подаются сигналы от клавиатуры управления, по цепи IR - от приемника ДУ. а по цепям MAIN_LED_ON/LED_N и LED_ON/LED_R подключаются индикаторные светодиоды. Двухкаскадный усилитель на транзисторах Q1300, Q1301 - усилитель сигналов ДУ.

Продолжение следует.

Все необходимые схемы к статье можно скачать здесь.

Автор: Геннадий Романов (г. Москва)

Источник: Ремонт и сервис