На базе шасси LC13E AA фирма PHILIPS производит телевизоры на TFT LCD-панелях с диагональю экрана 13", 15" и 20". Подробное описание этих панелей представлено в [1]. LCD-телевизоры как схемотехнически, так и конструктивно заметно отличаются от обычных аппаратов на ЭЛТ. В настоящей статье приведено описание принципиальной схемы. Сервисные режимы и некоторые характерные неисправности телевизионных приемников на шасси LC13E AA - это тема следующей статьи.

Общие сведения и конструкция шасси LC13E

Фирма PHILIPS использует шасси LC13E AA в следующих моделях телевизионных приемников: 13PF7835/12, 13PF7835/58, 15HF7835/22, 15HF7835/22Z, 20HF7835/22, 20HF7835/22Z, 20PF7835/12, 20PF7835/58 и т.п.

В телевизорах, собранных на шасси LC13E AA, применяются TFT LCD-панели LC130V01, LC150X01 и LC201V02 производства LG.PHILIPS LCD Co., Ltd, параметры и характеристики которых приведены в [1].

Главные отличия LC150X01 от остальных двух панелей - это разрешающая способность и интерфейс. Поэтому в телевизорах с этой панелью используется дополнительное масштабирующее устройство (Scaler Board).

Телевизоры на шасси LC13E AA обеспечивают прием до сотни телевизионных каналов в стандартах PAL B/G, PAL D/K, SECAM B/G, SECAM D/K и SECAM L/L', прием стереофонического звукового сопровождения 2CS BG (GERMAN STEREO) и NICAM B/G, D/K, L. Кроме того, эти аппараты имеют встроенный полный диапазон FM радиовещания. Остальные особенности, параметры и характеристики телевизоров с разной диагональю экрана на шасси LC13E AA сведены в табл.1.

Таблица 1. Особенности, параметры и характеристики телевизоров с разной диагональю экрана на шасси LC13E AA

Параметры | 13" | 15" | 20" |

Разрешение | 640x480 VGA | 1280x768 XGA | 640x480 VGA |

Угол обзора | 120°х90° | 176°х170° | 176°x170° |

Выходная мощность УМЗЧ | 2x3 Вт | 2x3 Вт | 2x5 Вт |

Потребляемая мощность | 35 Вт | 50 Вт | 60 Вт |

Потребляемая мощность в дежурном режиме | 1 Вт | ||

Сетевой адаптер переменного тока | Сеть: ~100...240 В, 1,5 А | ||

Тип SA165A-1250V-3 | Тип AD3591 | ||

Выход: 12 В ±0,6 В, 60 Вт | Выход: 24 В ±1,2 В, 120 Вт | ||

Масса | 4,5 кг | 5 кг | 8,5 кг |

Габаритные размеры | 344x322x65 мм | 377x361x70 мм | 477x435x81 мм |

Телевизионное шасси LC13E AA собрано на пяти платах:

При обозначении деталей на принципиальных схемах фирмы PHILIPS используются, как правило, только цифры. Что они обозначают, описано в [2].

Узлы, обозначение которых начинается с одних и тех же букв, находятся на одной и той же плате. Неразрывные соединения между ними изображены как утолщенные линии. Входящие и выходящие из этих линий более тонкие линии имеют смысловые сокращенные обозначения сигналов (например, AGC), а также указатели направления в виде стрелок и обозначения узлов, показывающих куда или откуда приходит этот провод.

Плата A (TV Board) условно разделена на 11 узлов:

Получить общее представление о плате А и проследить прохождение сигналов через эту плату можно по блок-схемам, приведенным на рис. 2 (см. архив) и рис. 3.

Рис. 3. Блок-схема управления ТВ (TV Control)

Плата С условно разделена на 5 узлов:

Получить общее представление о плате С и проследить прохождение сигналов через нее можно по блок-схеме, приведенной на рис. 4.

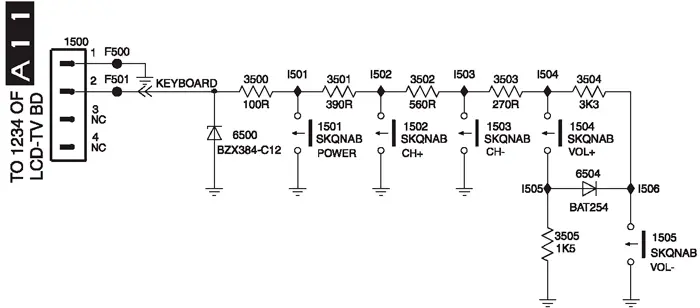

На плате E (верхней панели управления) распложены только 5 кнопок локальной клавиатуры с деталями обвязки (рис. 18).

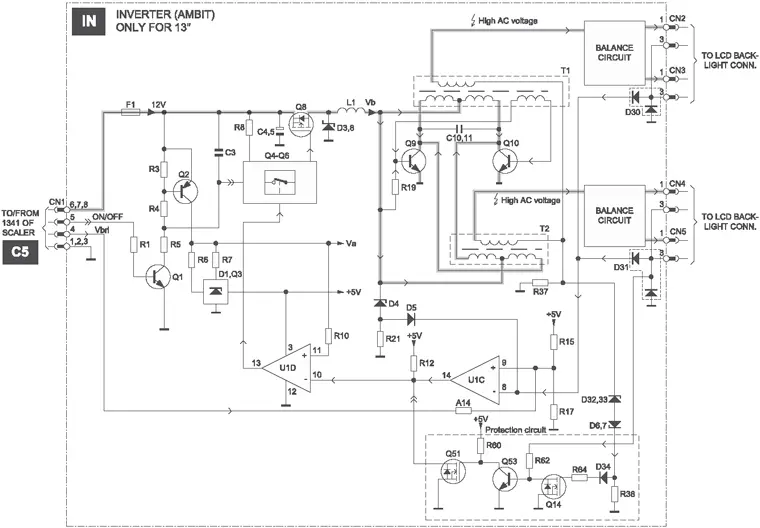

На плате IN (плате инвертора) расположена схема питания и управления включением ламп подсветки. Для разных панелей схемные решения инвертора разные. Причем, в телевизорах с диагональю 15 и 20 дюймов эта плата условно разделена на два узла IN1 и IN2. Получить общее представление о плате IN для телевизора с диагональю экрана 13 дюймов можно по рис. 5.

Рис. 5. Блок-схема платы инвертора (Inverter Panel)

Со схемами и подробным описанием инверторов для разных LCD-панелей телевизионного шасси LC13E можно ознакомиться в статье [3], а о других схемных решениях инверторов можно прочитать в [4].

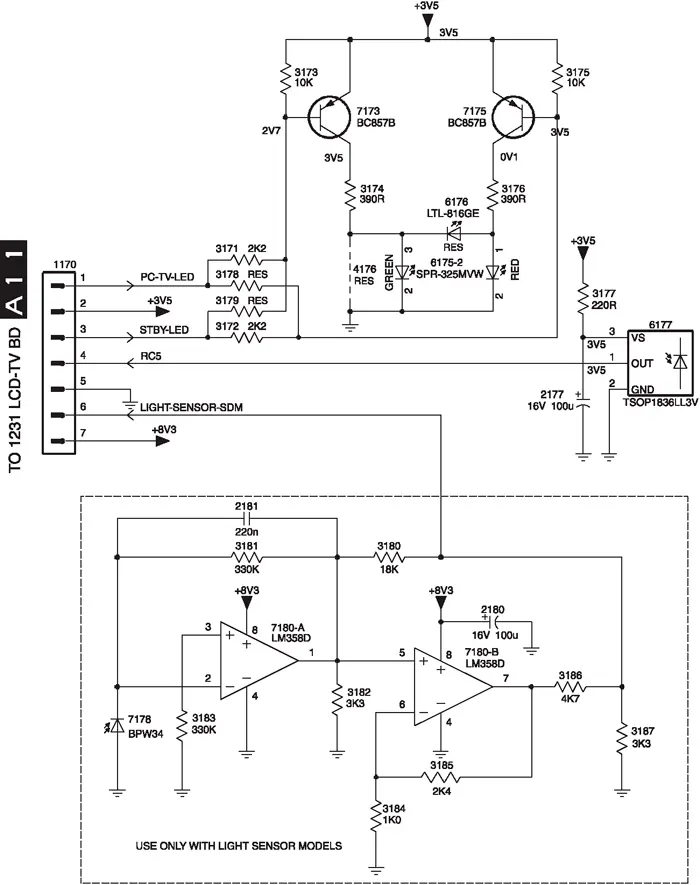

На плате J (передней панели светодиодной индикации) расположены светодиоды индикации режимов со схемой управления, ИК приемник дистанционного управления, а в некоторых моделях на этой плате установлен датчик освещенности и усилитель сигнала этого датчика.

Цепи питания узлов телевизионного шасси LC13E AA можно проследить по рис. 6.

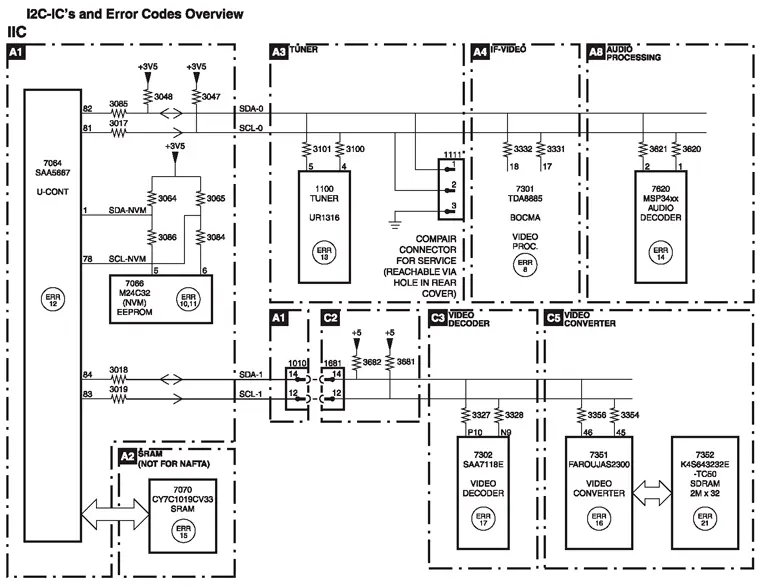

В телевизорах на шасси LC13E AA используется процессор управления 7064 типа SAA5667, который обменивается информацией и управляет другими микросхемами с помощью трех двухпроводных шин I2C.

Проследить цепи шин I2C всего шасси можно по рис. 7.

Рис. 7. Цепи управляющих шин I2C телевизионного шасси LC13E AA (I2C-IC's)

Принципиальная схема и работа телевизионного шасси LC13E AA

Узел тюнера A3

Полезный сигнал, принятый антенной, преобразуется в сигналы ПЧ изображения и звука в тюнере с синтезатором частоты 1100 типа UR1316 (см. рис. 8).

Управление тюнером осуществляется по шине I2C процессором 7064 (узел А1). Выв. 4 тюнера - это линия тактовых импульсов (SCL) шины I2C, а выв. 5 - линия данных (SDA).

Напряжение питания 5,3 В поступает на выв. 3, 6 и 7 тюнера.

Для питания варикапов (выв. 9) используется повышенное напряжение, которое формируется DC/DC-преобразователем, состоящим из генератора на транзисторе 7120, выпрямителя с удвоением напряжения на диодах 6120 и стабилитрона 6101.

Тюнер имеет расширенный диапазон FM-радиовещания, сигнал ПЧ (SIF-FM) которого с выв. 10 через УПЧ на транзисторах 7131 и 7130 поступает на узел процессора звука (A8). С выв. 11 тюнера сигнал ПЧ (IF-TER) поступает на полосовые фильтры на поверхностных акустических волнах (ПАВ) в узел А5 (см. рис. 9 в архиве).

Фильтр ПАВ узла A5

В телевизорах, которые производятся для Европы, установлено два фильтра ПАВ: 1452 на входе УПЧИ и 1454 на входе УПЧЗ квази-параллельного канала звука (QSS). Транзисторный ключ 7452 обеспечивает коммутацию стандартов. Он закрыт в режимах DK и BG.

Симметричные сигналы ПЧ с фильтров ПАВ поступают на УПЧИ (VIF1, VIF2) и УПЧЗ (SIF1, SIF2) в узел А4 (см. рис. 10 в архиве и рис. 2).

Узел A4 (IF-VIDEO - SYNC-CHROMA).

Общие положения

Узел УПЧИ, синхронизации и цветности A4 шасси LC13E AA собран на микросхеме 7301 типа TDA8885. Эту микросхему можно встретить в ряде телевизоров на ЭЛТ, например в телевизионном шасси 11AK33.

На принципиальной схеме узла A4 (рис. 10) микросхема 7301 условно разделена на три части (секции):

Радиоканал и канал звука, секция 7301-A (IF-VIDEO) микросхемы TDA8885

Симметричный сигнал ПЧ изображения с фильтра ПАВ поступает на дифференциальный вход УПЧИ БИС 7301-A (выв. 1 и 2), где он усиливается и детектируется. 2301 и 3303 - элементы внешнего фильтра ФАПЧ видеодетектора. Управляющее напряжение АРУ выводится из БИС 7301-A на тюнер через выв. 7 и фильтр (2302, 3302, 3305). После детектирования и усиления ПЦТС выводится из секции 7301-A микросхемы через выв. 16 и эмиттерный повторитель (ЭП) на транзисторе 7302.

Секция 7301-A содержит также квазипараллельный канал звука (QSS), на дифференциальный вход которого (выв. 8 и 9) поступает сигнал ПЧЗ от фильтра ПАВ 1454. Канал звука имеет собственную схему АРУ, конденсатор фильтра которой подключен к выв. 10. Сигнал ПЧ звука (SIF-TV) со стереосоставляющими с выхода канала QSS (выв. 11) через ЭП (7303) снимается на узел процессора звука A8. В режиме моно, а также при работе в стандарте L/L', НЧ сигнал звука, обозначенный на схеме как PIP-AUDIO, будет сниматься на процессор звука с выв. 27 секции 7301-A.

Синхропроцессор, секция 7301-C (SYNC) микросхемы TDA8885

Синхропроцессор этой микросхемы обеспечивает генерацию, формирование и синхронизацию строчных и кадровых запускающих импульсов, а также формирование стробирующих импульсов. Для синхронизации строк и кадров синхропроцессор выделяет синхросмесь из ПЦТС, который поступает на него внутри микросхемы с предварительного. Строчная синхронизация секции 7301-C микросхемы TDA8885 имеет две петли схемы АПЧФ. Фильтр АПЧФ1 (3317, 2317, 2318) подключен к выв. 59, а конденсатор фильтра АПЧФ2 2320 - к выв. 58. При стандартном включении через выв. 63 и 64 этой микросхемы должны выводиться противофазные кадровые пилообразные импульсы, конденсатор ГПН должен быть подключен к выв. 4 7301-С, а токозадающий линеаризующий резистор - к выв. 5. В этом шасси кадровый импульс должен иметь прямоугольную форму, поэтому вместо конденсатора ГПН к выв. 4 подключен резистор 3329. Кадровые импульсы отрицательной полярности (V-SYNC) снимаются с выв. 64 и поступают на узел А1, а положительные строчные импульсы (LINEDRIVE1) с выв. 56 микросхемы 7301-C поступают на узел А5. Для "нейтрализации" схем EW-коррекции и защиты микросхемы к выв. 63 подключен резистор 3322, а к выв. 3 - делитель напряжения на резисторах 3318 и 3319, заблокированный конденсатором 2319.

Электронный коммутатор внешних видеовходов (EXT. VIDEO SELECT) узла А5

Схема этого узла изображена на рис. 9.

Коммутатор собран на микросхеме 7401 типа 74HC4053 и ЭП на транзисторах 6412, 6415. На электронный коммутатор приходит пять сигналов с входных разъемов узла A11 (SCART IO): Y-CVBS-SC2_AV2-IN, CVBS-SC1_AV1-IN, Y-CVBS-FRONT-IN, C-FRONT-IN и C-SC2_SVHS-IN. Эти сигналы переключаются на входы гребенчатого фильтра А6 и внутреннего коммутатора видеосигналов микросхемы TDA8885 (узел А4). После коммутации для ПЦТС на схеме используется обозначение MAIN-CVBS-EXT-IN, а для сигнала цветности - MAIN-C-EXT-IN. Сигналы переключения SEL-MAIN-FRNT-RR и SEL-MAIN-FRNT-RR поступают на выв. 10, 11 и 9 микросхемы 7401 с выв. 4 и 55 микроконтроллера (МК) 7064 узла A1.

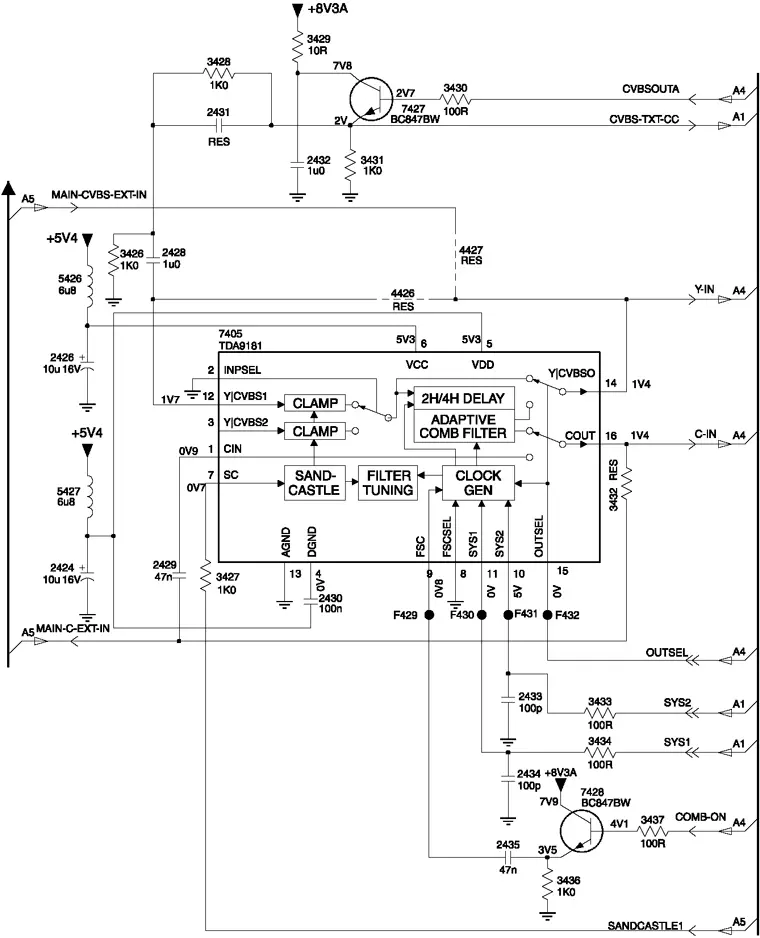

Узел гребенчатого фильтра A6 (ANALOG COMB FILTER)

Принципиальная схема этого узла показана на рис. 11.

Рис. 11. Принципиальная схема узла гребенчатого фильтра A6 (ANALOG COMB FILTER)

Узел гребенчатого фильтра A6 (ANALOG COMB FILTER) обеспечивает разделение ПЦТС на сигналы яркости и цветности. ПЦТС для узла А6 снимается с выхода коммутатора микросхемы 7301-B (выв. 54, см. рис. 10). Выделенный фильтром яркостной сигнал возвращается в микросхему 7301-B на выв. 21, а сигнал цветности - на выв. 20.

Основой узла А6 является специализированная микросхема 7405 типа TDA9181.

Узел гребенчатого фильтра содержит также два ЭП: 7427 используется в цепи подачи ПЦТС на выв. 12, а 7428 - в цепи подачи опорного сигнала поднесущей цветности на выв. 9 7405.

У этой микросхемы используется только один вход ПЦТС - выв. 12, другой вход (выв. 13) не подключен, а вход сигнала цветности (выв. 1) заземлен конденсатором 2429. На вход управления переключением входов (выв. 2) подан уровень лог. 0. На вход управления переключением выходных сигналов OUTSEL (выв. 15) поступает сигнал с выв. 22 микросхемы 7301-B (А4).

В зависимости от системы ТВ параметры гребенчатого фильтра изменяются логическими уровнями на выв. 10 и 11 микросхемы 7405 TDA9181 (см. табл. 2), которые поступают туда с МК (узел А1).

Таблица 2. Выбор системы ТВ для микросхемы гребенчатого фильтра TDA9181

Выводы | Система ТВ | ||

11 (SYS1) | 10 (SYS2) | ||

Уровни управляющих напряжений | Низкий | Низкий | PAL M |

Низкий | Высокий | PAL B, G, H, D, I | |

Высокий | Низкий | NTSC M | |

Высокий | Высокий | PAL N | |

Сигнал яркости поступает на узел А4 с выв. 14 микросхемы 7405, а сигнал цветности - с выв. 16 этой же микросхемы.

Каналы цветности и яркости с матрицами и усилителями RGB, секция 7301-B (CHROMA) микросхемы TDA8885 (узел А4)

Вернемся опять к схеме узла А4 (рис. 10). На входе секции 7301-B микросхемы TDA8885 стоит коммутатор видеовходов, который имеет четыре входа и два выхода для внешних сигналов.

При работе в режиме телевизора ПЦТС с входа CVBSINT (выв. 24) через внутренний коммутатор поступает на входы канала яркости и декодера цветности в составе 7301-B. Точно так же коммутируются внешние ПЦТС с остальных входов. Только в режиме AV3 разделенные гребенчатым фильтром А6 сигналы яркости и цветности коммутируются в соответствующие каналы с выв. 21 (Y3) и 20 (C3). С выв. 49 7301-B снимается опорный сигнал поднесущей цветности COMB-ON. Наличие этого сигнала обеспечивает включение гребенчатого фильтра, а отсутствие - выключение.

Для синхронизации работы мультистандартного декодера цветности и всей микросхемы 7301 используется генератор с внешним кварцевым резонатором 1330 (12 МГц), подключенным к выв. 51 и 52.

Полученные в результате декодирования цветоразностные сигналы красного V и синего U вместе с сигналом яркости Y поступают на коммутатор, на который через выв. 41, 42 и 43 7301-B приходят также сигналы R-SC1_V-IN, B-SC1-INJJ-IN и G-SC1-IN_Y-IN от разъема SCART. Сигналы с разъема SCART включаются высоким уровнем (1...3 В) сигнала FBL-SC1-IN, поступающим на выв. 44 7301-B от внешнего устройства через контакт 16 разъема SCART.

Затем сигналы YJV поступают на RGB-матрицу, где из них формируются RGB-сигналы и примешиваются RGB-сигналы графики (OSD) и телетекста. Выв. 35 7301-B - это вход R|1, 36 - вход G|1, 37 - вход B|1, а 38 - вход бланкирую-щего сигнала BL|1. В микросхеме TDA8885 производятся операции "расширения" черного и белого для улучшения качества изображения. Накопительный конденсатор схемы расширения белого 2339 подключен к выв. 19 7301-B.

После усиления RGB-сигналы выводятся из микросхемы 7301-B через выв. 33, 32, 31 и через эмиттерные повторители 7350, 7353, 7356 вводятся в узел А1 (см. рис.16), а затем через разъем 1010 (контакты 1, 3, 5) они поступают на узел С2 (см. рис. 20).

HISTROGRAM-корректор сигналов цветности и яркости, узел А5

HISTROGRAM-корректор (процессор) собран на микросхеме 7403 типа TDA9171 (см. рис. 9). Он обрабатывает сигналы YJV, которые снимаются на его входы с выв. 40 (сигнал Y-MAIN), выв. 45 (сигнал J-MAIN) и выв. 46 (сигнал V-MAIN) секции 7301-B узла А4 (рис. 10). После обработки эти сигналы заводятся в эту же микросхему через выв. 39 (сигнал Y-HISTROGRAM), выв. 47 (сигнал J-HISTROGRAM) и выв. 48 (сигнал V-HISTROGRAM).

Для улучшения качества изображения микросхема 7403 TDA9171 (рис. 9) осуществляет нелинейную 5-сегментную гистограммную коррекцию сигналов YJV и "расширение" синего. Для каждого из 5-ти сегментов гистограммы используется свой запоминающий конденсатор (2475,..., 2478) и общий конденсатор 2473, задающий постоянную времени гистограммной модификации сигналов. Для включения HISTROGRAM-корректора на выв. 1, 4 и 20 микросхемы 7403 должен быть низкий потенциал, который создается технологическими перемычками (SMD-резисторы 0 Ом) или транзисторным ключом 7473 (через разделительные диоды 6470, 6471, 6472).

HISTROGRAM-корректор устанавливается не на все телевизоры (опция), поэтому при отсутствии микросхемы 7403 TDA9171 и элементов ее обвязки вместо них устанавливаются перемычки 4470, 4471 и 4472.

Узел процессора звука A8 (AUDIO PROCESSING)

Принципиальная схема этого узла показана на рис. 12.

Основой узла A8 телевизоров на шасси LC13E служит популярная микросхема MSP3410G (7620) фирмы Micronas (см. [5, 6]). В позиции 7620 может устанавливаться микросхема MSP3411G. Она отличается от MSP3410G только наличием функции Virtual Dolby. Управление БИС 7620 осуществляется процессором управления по шине I2C.

Сигнал второй ПЧ звука (SIF) с узла А4 поступает на выв. 50, а сигнал ПЧ радиовещательного FM-диапазона (SIF-FM) - на выв. 52 7620. На НЧ входы этой микросхемы поступают следующие НЧ сигналы звукового сопровождения:

Все перечисленные выше разъемы входят в состав узла входов-выходов SCART А11 (SCART IO), схема которого представлена на рис. 13.

Все НЧ сигналы, поступившие на процессор звука 7620, попадают на коммутатор входов, а затем оцифровываются. Оцифровываются также сигналы ПЧ, а затем де-модулируются и обрабатываются в соответствии с выбранным алгоритмом. После ЦАП и регуляторов громкости сигналы выводятся из процессора через выв. 20 и 21 на двухканальный УМЗЧ (узел А9). Нерегулируемые звуковые сигналы через выв. 25, 26 и 28, 29 7620 поступают на выходные разъемы в узел А11.

Узел задержки сигнала звука A7 (AUDIO DELAY LINE)

LCD-телевизоры с цифровой обработкой сигналов изображения и конвертированием форматов, из-за сложности обработки, имеют один специфический недостаток - это задержка сигналов изображения (видеосигналов) относительно сигналов звука. В шасси LC13E задержка сигналов изображения относительно сигналов звукового сопровождения составляет 80 мс. Это незначительно проявляется на крупных планах в виде небольшого отставания артикуляции говорящего от самой речи. Для устранения этого недостатка следует производить так называемую "синхронизацию губ" ("lip sync"), т.е. задержку сигнала звука на те же 80 мс. "Синхронизация губ" выполняется узлом A7 (см. рис. 14).

Для обмена оцифрованными сигналами звука между узлами звукового процессора А8 и задержки А7 используется шина I2S. Мультиплексированные оцифрованные 16-битные сигналы правого и левого каналов звука I2S_DA_OJT в последовательном коде с частотой передачи цикла 32 кГц снимаются с выв. 5 процессора 7620 (рис. 12) и поступают на выв. 2 микросхемы 7604 узла задержки А7 (см. рис. 14).

Аналогичный, но задержанный в этом узле на 80 мс, сигнал I2S_DA_IN1 снимается с выв. 15 микросхемы 7605 (рис. 14) и поступает на выв. 6 процессора 7620. Для синхронизации узлов А7 и А8 с выв. 3 7620 снимаются тактовые импульсы с частотой следования 1,024 МГц и подаются на узел А7.

Узел задержки сигнала звука A7 собран на пяти микросхемах и одном транзисторе. Транзистор 7610 - это инвертор тактовых импульсов. Две из указанных выше микросхем 7604 и 7605 типа 74HCT573D - 8-разрядные буферные регистры с защелкой и тремя состояниями.

Микросхема 7604, за счет связей между триггерами, организована как сдвиговый регистр. Именно на эту микросхему (на выв. 2) по шине шина I2S поступает входной сигнал. Восьмиразрядный двоичный код, сдвигающийся с каждым тактовым импульсом на один разряд, с выходов (выв. 19, 18, ..., 12) регистра 7604 поступает на информационные выводы (входы/выходы) микросхемы статического ОЗУ 7603 типа CY62256. Эта микросхема позволяет запомнить 32768 слов по 8 бит. Выводы выбора кристалла 20 (CE_) и разрешения включения выходов 22 (OE_) активированы постоянно, так как соединены с корпусом. Вывод разрешения записи 27 (WE_) активируется при низком уровне приходящих на него тактовых импульсов. При этом выв. 19, 18, ..., 12 включаются как входы. Адреса ячеек памяти ОЗУ 7603 в двоичном коде (15 разрядов: А0, А1, ...А14) перебираются последовательно один за другим с помощью 15-разрядного двоичного счетчика, организованного на микросхемах 7601 и 7602 типа TC74HC590AF. При высоком уровне тактовых импульсов на выв. 27 (WE_) информационные выводы микросхемы ОЗУ 7603 работают как выходы. При этом высокий уровень тактовых импульсов на выв. 1 и 11 микросхемы 7604 типа 74HCT573D переводит ее выходы в высокоимпедансное состояние. Поэтому на входы второй микросхемы 74HCT573D с позиционным номером 7605 поступают логические уровни с информационных выходов микросхемы ОЗУ Процессор звука организовывает работу узла А7 так, что полная запись и готовность к считыванию 16-разрядного слова по принципу FIFO ("первый вошел - первый вышел") занимает 16 мс. Задержка сигналов звукового сопровождения на 80 мс организована за пять шагов FIFO по 16 мс. Каждый шаг сохраняется в триггерах выходного буфера 7605. Выбрать соответствующий шаг, а значит и задержку сигнала звука кратную 16 мс, можно, установив одну из перемычек 4610, ..., 4617. Для обеспечения задержки 80 мс должна быть установлена только одна перемычка 4614.

Узел УМЗЧ A9 (AUDIO AMPLIFIER)

В телевизорах с диагональю экрана 13" и 15" в качестве стереофонического усилителя мощности используется микросхема AN7522N (2 х 3 Вт), а в телевизорах 20" - микросхема AN5277N (2 х 5 Вт).

Принципиальная схема этого узла на микросхеме AN7522N показана на рис. 15.

Микросхема AN7522N - двухканальный УМЗЧ с мостовым выходом и возможностью регулировки громкости. Она питается напряжением 12 В и имеет минимум элементов обвязки. Регулировка громкости в УМЗЧ не производится, эту функцию выполняет процессор звука. Вывод регулировки громкости 9 микросхемы 7731 используется для блокировки звука в дежурном режиме и при пониженном напряжении питания с помощью двухвходового логического элемента "И" секция 7732-A микросхемы 74LCV08AD. Два других логических элемента "И" этой микросхемы (7732-C и 7732-D), включенные параллельно, и транзисторный ключ 7744 используются для формирования сигнала OJTjMJTE, который управляет ключами на цифровых транзисторах 7674 и 7675 в узле А8. Эти ключи шунтируют НЧ сигналы звука, поступающие на выходные разъемы в узел А11. Транзисторный ключ 7756 (узел УМЗЧ А9) формирует сигнал HP-SIDE-DET при включении головных телефонов в разъем 1731 и замыкании контактов 5 и 6 этого разъема.

Микросхема УМЗЧ типа AN5277N устанавливается в телевизорах с диагональю 20", и представляет собой двухканальный УМЗЧ с полумостовым (несимметричным) выходом. Напряжение питания этой микросхемы составляет 24 В.

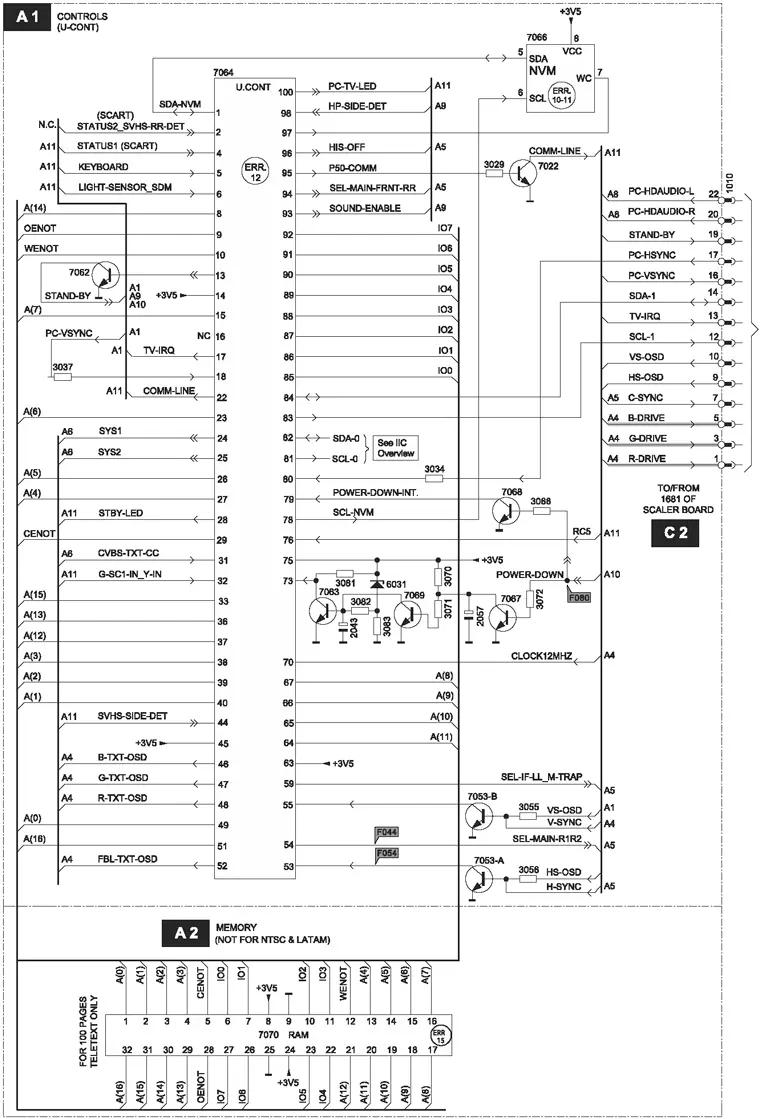

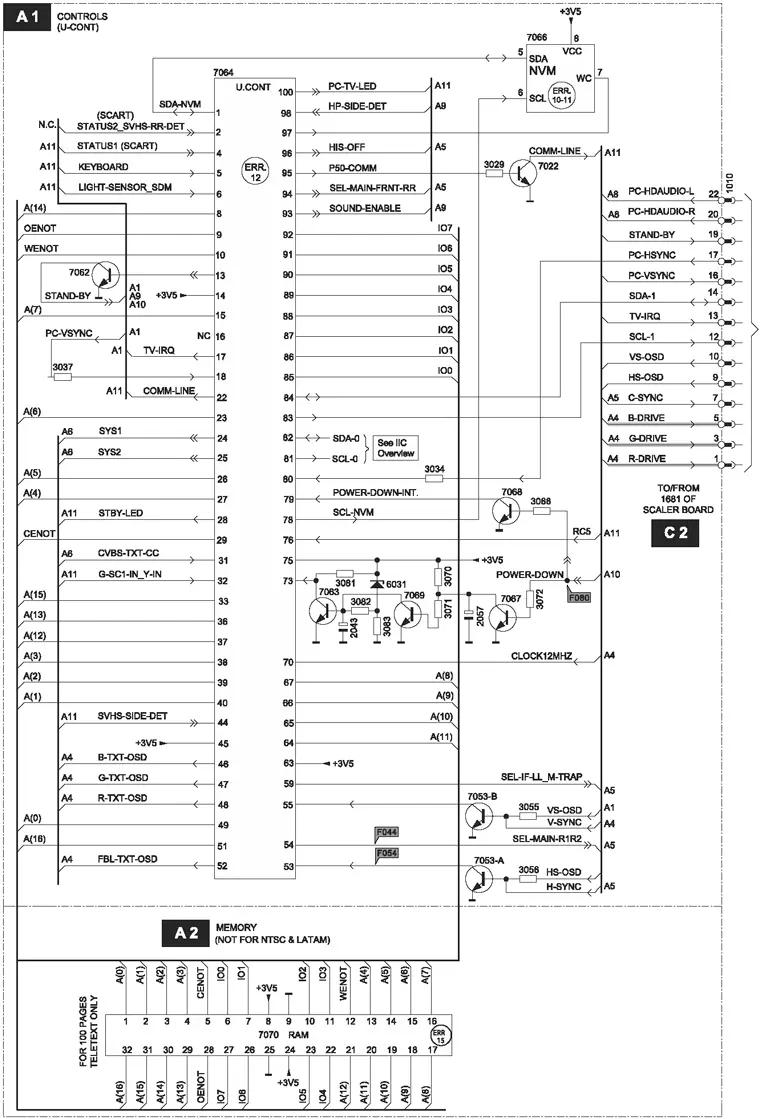

Узлы процессора управления и телетекста A1 (U_CONT) и дополнительной памяти A2 (MEMORY FOR 100-PG TELETEXT)

Основой этого узла для европейских моделей телевизоров является микроконтроллер 7064 типа SAA5667.

Эта микросхема имеет порты ввода/вывода для трех шин I2C, вход для обработки команд ДУ (RC5), выходы для управления светодиодными индикаторами. МК обеспечивает следующие функции:

Принципиальная схема узла A1 (JjCONT) приведена на рис. 16.

Микросхема SAA5667 изготовлена в 100-выводном корпусе типа LQFP100 на 8-разрядном микропроцессорном ядре 80С51.

Работа телевизора при включении начинается с формирования положительного импульса сброса (команда RESET) схемой сброса на элементах 7063 (BC847BW) и 6031 (BZX284-C2V4).

При наличии неисправности, которая приводит к уменьшению напряжения питания телевизора 12 (24) В от внешнего БП, предусмотрена блокировка МК, которая собрана на транзисторах 7067 и 7069. Схема блокировки использует сигнал POWER-DOWN (низкий уровень - активный), который поступает из узла А10. Инерционность схемы блокировки задается RC-цепью (3070, 2057). Из сигнала POWER-DOWN с помощью транзистора 7068 формируется инверсный ему сигнал POWER-DOWN-INT, который поступает на вход прерываний P1.2/INT0 (выв. 79 7064). Тактовый сигнал частотой 12 МГц не генерируется микроконтроллером, а поступает на выв. 70 этой микросхемы с выв. 52 секции 7301-В микросхемы TDA8885 узла A4 (рис. 10).

Процессоры серии SAA56хх имеют только две изначально организованные шины I2C (выв. 81 (P1.6/SCL0), выв. 82 (P1.7/SDA0), выв. 83 (P1.4/SCL1), выв. 84 (P1.5/SDA1)). Первая из них обеспечивает обмен информацией с тюнером 1100 (узел А3), видеопроцессором 7301 (узел A4) и звуковым процессором 7620 (узел A8), а вторая - с видеодекодером 7302 (узел C3) и видеоконвертором 7351 (узел C5).

Для управления микросхемой энергонезависимой памяти 7066 типа M24C32 в МК программно организована третья шина I2C (выв. 1 (P2.7/PWM6 - SDA-NVM) и выв. 78 (P1.1/T0 - SCL-NVM)). Сигнал разрешения записи в эту микросхему снимается с выв. 97 7064.

Выв. 5 (P3.2/ADC2) микросхемы 7064 используется как вход АЦП сигнала от локальной клавиатуры телевизора (KEYBOARD), а выв. 6 - как вход АЦП сигнала от датчика освещенности (LIGHT-SENSOR_SDM). Сигнал STAND-BY - это инвертированный транзистором 7062 сигнал от выв. 13 (P0.5) 7064.

RGB-сигналы графики (OSD) и телетекста снимаются на узел А4 со следующих выводов МК:

Для формирования этих сигналов необходимы строчные и кадровые импульсы, которые поступают на выв. 53 (HSYNC) и выв. 55 (VSYNC) микросхемы 7064 через инверторы 7053-A и 7053-B. Для работы телетекста на выв. 32 и 31 7064 подается ПЦТС. Для получения 100-страничного телетекста необходима дополнительная микросхема ОЗУ, которая выделена на схеме в отдельный узел - А2 (см. рис. 17).

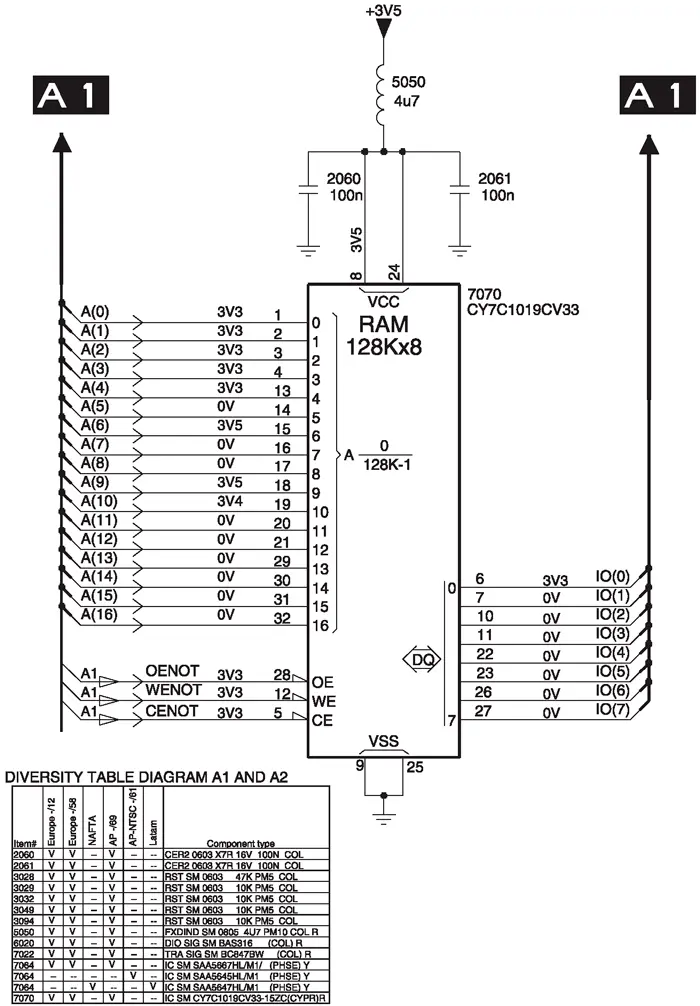

Рис. 17. Принципиальная схема узла дополнительной памяти для 100-страничного телетекста A2 (MEMORY FOR 100-PG TELETEXT)

Необязательный узел дополнительной памяти A2 реализован на микросхеме статического ОЗУ объемом 128 х 8 кбит 7070 типа CY7C1019CV33. Эта микросхема имеет 17-разрядную адресную шину (выв. 1-4, 13-21, 29-32) и 8разрядную шину данных (выв. 6, 7, 10, 11, 22, 23, 26, 27). Микросхема 7070 имеет также выводы выбора кристалла CE (19), разрешения включения выходов OE (28) и разрешения записи WE (12). Все эти выводы ОЗУ 7070 соединены только с соответствующими выводами МК 7064 (см. рис. 16). При этом 17-разрядная адресная шина МК (А0, А1, ..., А16) - это выв. 49, 40, 39, 38, 27, 26, 23, 15, 67, 66, 65, 64, 37, 36, 8, 33, 51, а 8-разрядная шина данных - выв. 85-92. Назначение некоторых выводов МК указывалось при рассмотрении других узлов телевизора, а назначение остальных его выводов легко проследить по принципиальной схеме.

Верхняя панель управления E (Top Control Panel) и передняя панель светодиодной индикации J (Front LED Panel)

Эти две платы схемотехнически просты (см. рис. 18 и 19).

Рис. 18. Принципиальная схема платы верхней панели управления E (Top Control Panel)

Рис. 19. Принципиальная схема платы передней панели светодиодной индикации J (Front LED Panel)

На плате Е размещены пять кнопок управления, ограничивающие резисторы и защитные диоды. Выход этой платы через контакты 2 разъемов 1500 (E) и 1234 (А11) связан с выв. 5 7064.

На плате J расположен ИК приемник 6177, ключи светодиодного индикатора 7173, 7175 и двухцветный (красный-зеленый) двойной светодиод 6175 типа SPR-325MVW. Третий светодиод 6176 обычно не устанавливается. Сигналы управления светодиодами снимаются с выв. 28 и 100 микроконтроллера 7064 и поступают на плату J через узел А11. Кроме того, на плату J может устанавливаться фотодатчик (фотодиод) освещенности 7178 типа BPW34 с усилителем на двух ОУ микросхемы 7180 типа LM358D. Сигнал с выхода этого усилителя поступает на выв. 6 МК 7064.

Узел входов-выходов и интерфейса C2 (I/O & INTERFACE)

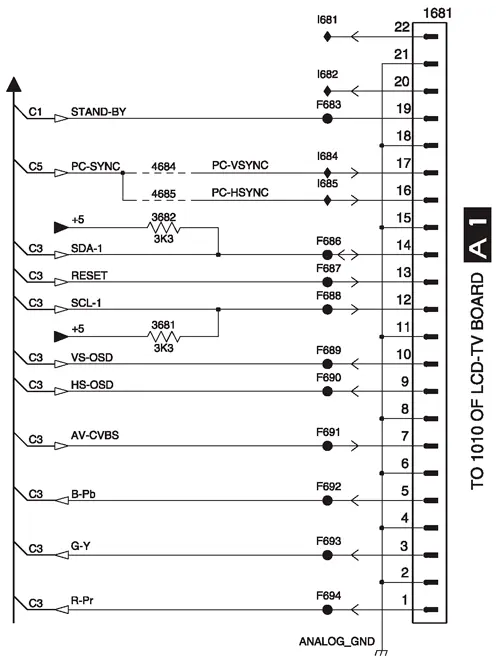

Узел С2 - это 22-контактный разъем 1681 (см. рис. 20), с помощью которого плата C соединяется с платой A. Ответная часть этого разъема 1010 изображена на схеме узла A1 (см. рис. 16).

Рис. 20. Принципиальная схема узла входов-выходов и интерфейса C2 (I/O & INTERFACE)

Обозначения сигналов на контактах разъемов 1681 и 1010 не совпадают - см. табл. 3.

Таблица 3. Назначение контактов разъемов 1010 (узел A1) и 1681 (узел C2)

№ вывода | Обозначеные сигнала | Назначение (относительно платы С) | |

1010 (A1) | 1681 (C2) | ||

1 | R-DRIVE | R-Pr | Вход сигнала красного |

2, 4, 6, 8, 11, 15, 18, 21 | Корпус | ||

3 | G-DRIVE | G-Y | Вход сигнала зеленого |

5 | B-DRIVE | B-Pb | Вход сигнала синего |

7 | C-SYNC | AV-CVBS | Вход синхросигнала |

9 | HS-OSD | HS-OSD | Выход строчных импульсов |

10 | VS-OSD | VS-OSD | Выход кадровых импульсов |

12 | SCL-1 | SCL-1 | Линия тактовых импульсов шины I2C |

13 | TV-IRQ | RESET | Сигнал сброса для 7351 (узел С5) |

14 | SDA-1 | SDA-1 | Линия данных шины I2C |

16 | PC-VSYNC | PC-VSYNC | Выход кадровых синхроимпульсов |

17 | PC-HSYNC | PC-HSYNC | Выход строчных синхроимпульсов |

19 | STAND-BY | STAND-BY | Вход сигнала выключения ТВ |

20 | PC-HDAUDIO-R | Не задействованы | |

22 | PC-HDAUDIO-L | ||

Узел видеодекодера C3 (VIDEO DECODER)

Узел видеодекодера C3 преобразует аналоговые сигналы RGB стандартного формата SDTV (Standard Definition Television - телевидение со стандартным разрешением) в цифровые RGB-сигналы того же стандартного формата. Возможность преобразования этих сигналов в формат VGA в узле С3 не используется.

Принципиальная схема этого узла изображена на рис. 21.

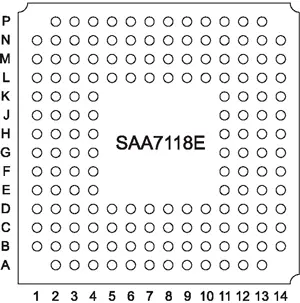

Основой узла С3 является микросхема 7302 типа SAA7118E, которая имеет 156-выводный корпус типа BGA. Расположение выводов микросхемы 7302 SAA7118E в корпусе BGA156 показано на рис. 22. Для питания этой микросхемы используется стабилизатор 3,3 В на микросхеме 7301 типа LD1117DT33.

Рис. 22. Расположение выводов микросхемы SAA7118E в корпусе BGA156

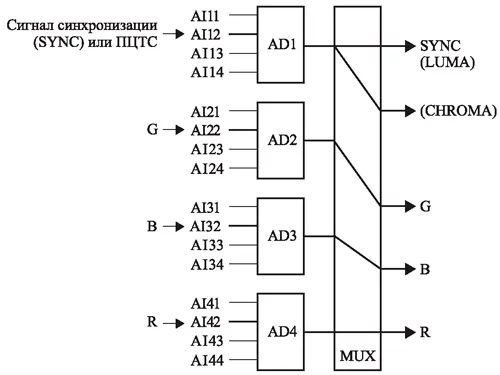

Микросхема SAA7118E - это многофункциональная микросхема с избыточными для шасси LC13E функциями. На входе этой микросхемы стоят четыре АЦП, которые могут быть программно сконфигурированы под различные входные сигналы и способы их дальнейшей обработки. В шасси LC13E программно выбран режим MODE31 (SRGB2). Конфигурация входных АЦП микросхемы SAA7118E в режиме MODE31 показана на рис. 23, а назначение задействованных выводов этой микросхемы, кроме выводов питания и корпуса, сведено в табл. 4.

Рис. 23. Включение входных АЦП микросхемы SAA7118E в режиме MODE31 (SRGB2)

Таблица 4. Назначение задействованных выводов микросхемы SAA7118E

№ вывода | Обозначение | Назначение |

M13 | FSW | Вход бланкирования, не используется (подключен на корпус) |

K1 | AI12 | Аналоговый вход 12 (вход 2 первого АЦП) |

K3 | AI1D | Симметричный (дифференциальный) вход АЦП1 (для выв. AI11, ..., AI14) |

G3 | AI22 | Аналоговый вход 22 (вход 2 второго АЦП) |

H1 | AI2D | Симметричный вход АЦП2 (для выв. AI21, ..., AI24) |

F2 | AI32 | Аналоговый вход 32 (вход 2 третьего АЦП) |

F1 | AI3D | Симметричный вход АЦП3 (для выв. AI31, ..., AI34) |

D2 | AI42 | Аналоговый вход 42 (вход 2 четвертого АЦП) |

D3 | AI4D | Симметричный вход АЦП4 (для выв. AI41, ..., AI44) |

P4 | LCC | Выход тактовых импульсов 27 МГц |

N10 | RST1 | Выход кадровых импульсов |

A3 | XTAL | Выводы подключения кварцевого резонатора 24,576 МГц |

B4 | XTALI | |

A8 | XPD0 | 8-разрядный выходной порт (X-PORT) |

B8 | XPD1 | |

A9 | XPD2 | |

B9 | XPD3 | |

A10 | XPD4 | |

B10 | XPD5 | |

A11 | XPD6 | |

C11 | XPD7 | |

A7 | XCLK | Вход/выход тактовых импульсов расширенного X-PORTа |

C7 | XRH | Вход/выход опорных строчных импульсов расширенного X-PORTа |

D8 | XRV | Вход/выход опорных кадровых импульсов расширенного X-PORTа |

C6 | TRSTN | Вход сброса теста (подключен на корпус) |

P12 | ALRCLK | Вывод выбора тактовой частоты (на шасси LC13E должен быть через резистор 4,7 кОм подключен на корпус) |

N9 | SCL | Шина I2C |

P10 | SDA |

Для вывода мультиплексированных видеосигналов RGB в параллельном коде на узел С5 используется 8-разрядный выходной порт X-PORT.

Узел конвертора форматов C5 (VIDEO CONVERTER)

Назначение этого узла - преобразование мультиплексированных цифровых видеосигналов RGB стандартного разрешения SDTV в раздельные цифровые видеосигналы RGB стандарта VGA (640x480 точек). Именно такие сигналы являются входными для панелей LC130V01 и LC201V02 (см. [1]).

Принципиальная схема узла конвертора форматов C5 изображена на рис. 24.

Кроме того, в этом узле осуществляются оперативные регулировки контрастности, насыщенности и четкости изображения.

Узел C5 собран на двух микросхемах. Одна из них - конвертор цифровых форматов 7351 типа FLI2300, а другая - 32-разрядное статическое ОЗУ (2Мх32) 7352 типа K4S643232E-TC50. Микросхема FLI2300 изготовлена в 208-вывод-ном корпусе PQFP Эта БИС работает по патентованным алгоритмам фирмы Farouja. Микросхема статического ОЗУ K4S643232E-TC50 изготовлена по КМОП-техно-логии в 86-выводном корпусе TSOP(II).

Принцип работы узла конвертора форматов C5 (VIDEO CONVERTER) заключается в том, что БИС 7351 записывает в ОЗУ 7352 входные оцифрованные сигналы стандартного разрешения (SDTV) с одной скоростью, а считывает сигналы из этого ОЗУ с другой скоростью в другом разрешении и формате (VGA, 640x480 точек).

Мультиплексированные видеосигналы RGB в параллельном коде со стандартным разрешением с выходного порта (X-PORT) микросхемы 7302 SAA7118E узла С3 поступают на входной восьмиразрядный порт БИС 7351 FLI2300 (выводы 198-205). С микросхемы 7302 SAA7118E узла С3 на выводы 206, 207, 208 БИС 7351 FLI2300 поступают также сигналы синхронизации. Для обмена информацией между БИС 7351 и ОЗУ 7352 используется 32-разрядная шина данных и 11-разрядная адресная шина.

Для управления процессом обмена данных используется шина управления, выводы 104, 105-111, 114 БИС 7351 и 16, 17-20, 22, 23, 28, 59, 67, 68, 71 БИС 7352.

Полученные в результате конвертирования восьмиразрядные оцифрованные ТТЛ сигналы RGB в параллельном коде выводятся из БИС 7351 на узел выходного интерфейса C4 через выв. 126, 127, 130-135 (сигнал B), выв. 136, 137, 140-145 (сигнал R) и выв. 148, 149, 150-155 (сигнал G).

Узел выходного интерфейса LVDS C4 (OUTPUT [LVDS])

К этому узлу отнесен выходной разъем 1501 (TTL-OUT), через который выходные сигналы RGB от узла C5 поступают на LCD-панель формата VGA (рис. 25). Назначение выводов этого разъема приведено в табл. 5.

Таблица 5. Назначение выводов разъема 1501 ТТЛ интерфейса для LCD-панелей LC130V01 и LC201V02

| № | Обозначение | Назначение | № | Обозначение | Назначение |

1 | - | Не используется | 22 | - | Корпус |

2 | FSHFCLC | Тактовые импульсы точек | 23 | G-Y-OUT5 | Старшие разряды сигнала зеленого |

3 | - | Корпус | 24 | G-Y-OUT6 | |

4 | FHSYNC | Строчные импульсы | 25 | G-Y-OUT7 | |

5 | FVSYNC | Кадровые импульсы | 26 | B-U-OUT0 | Младший разряд сигнала синего |

6 | - | Корпус | 27 | - | Корпус |

7 | R-V-OUT0 | Младшие разряды сигнала красного | 28 | B-U-OUT1 | Сигнал синего (четыре разряда из восьми) |

8 | R-V-OUT1 | 29 | B-U-OUT2 | ||

9 | R-V-OUT2 | 30 | B-U-OUT3 | ||

10 | R-V-OUT3 | 31 | B-U-OUT4 | ||

11 | R-V-OUT4 | 32 | - | Корпус | |

12 | - | Корпус | 33 | B-U-OUT5 | Старшие разряды сигнала синего |

13 | R-V-OUT5 | Старшие разряды сигнала красного | 34 | B-U-OUT6 | |

14 | R-V-OUT6 | 35 | B-U-OUT7 | ||

15 | R-V-OUT7 | 36 | - | Корпус | |

16 | G-Y-OUT0 | Младший разряд сигнала зеленого | 37 | FDE | Сигнал разрешения |

17 | - | Корпус | 38 | - | Корпус |

18 | G-Y-OUT1 | Сигнал зеленого (четыретразряда из восьми) | 39 | - | Напряжение питания (+12 В для 20,1" и +3,3 В для 13") |

19 | G-Y-OUT2 | 40 | - | ||

20 | G-Y-OUT3 | 41 | - | ||

21 | G-Y-OUT4 | 42 | - | Корпус |

В 15-дюймовых телевизорах с LCD-панелью формата XGA в узле C4 устанавливается дополнительный конвертор форматов на БИС 7501 типа DS90C385MTDX, который преобразует ТТЛ сигналы RGB в четыре дифференциальных сигнала интерфейса LVDS для подачи их на LCD-панель LC150X01. Кроме того, сигнал тактовых импульсов, сформированный микросхемой 7501, также преобразуется в дифференциальный (симметричный) сигнал и поступает на LC150X01. Описание интерфейса LVDS приведено в [1]. Назначение линий LVDS-интерфейса на выходах БИС 7501 типа DS90C385MTDX, выходном разъеме 1506 и входном разъеме LCD-панели LC150X01 приведено в табл. 6.

Таблица 6. Линии LVDS-интерфейса на выходах БИС 7501 типа DS90C385MTDX, выходном разъеме 1506 и входном разъеме LCD-панели LC150X01

Номера выводов | Обозначение выводов 7501 | Назначение | ||

7501 | 1506 | LC150X01 | ||

49 | 3, 5-9 | 7 | GND | Корпус |

48 | 2 | 5 | TXIN0- | Линия 0 LVDS-интерфейса (сигналы R0*-R5, G0) |

47 | 4 | 6 | TXIN0+ | |

46 | 10 | 8 | TXIN1- | Линия 1 LVDS-интерфейса (сигналы G1-G5, B0, B1) |

45 | 12 | 9 | TXIN1 + | |

43 | 11, 13-17 | 10 | GND | Корпус |

42 | 18 | 11 | TXIN2- | Линия 2 LVDS-интерфейса (сигналы B2-B5, DE, Hsync и Vsync) |

41 | 20 | 12 | TXIN2+ | |

33 | 19, 21-25 | 13 | GND | Корпус |

40 | 34 | 14 | TXCLKIN- | Линия тактовых импульсов LVDS-интерфейса |

39 | 36 | 15 | TXCLKIN+ | |

38 | 26 | 17 | TXIN3- | Линия 3 LVDS-интерфейса (сигналы R6, R7, G6, G7, B6, B7, RES) |

37 | 28 | 18 | TXIN3+ | |

36, 35 | 27, 29-33 | 19 | GND | Корпус |

20 | GND | |||

- | 35 | 16 | - | |

- | 37 | 3 | - | |

- | 38 | 4 | - | |

- | 39 | 1 | - | Напряжение питания +12 В (PAN-VCC) |

- | 40 | 2 | ||

* Цифры здесь и далее в последнем столбце таблицы - это номера разрядов двоичного кода соответствующего сигнала.

Таблица 7. Напряжения питания телевизоров на шасси LC13E и используемых в них LCD-панелей

Диагональ экрана | 13" | 15" | 20" |

Напряжение питания телевизора | 12 В | 12 В | 24 В |

Напряжение питания LCD-панели (PAN-VCC) | 3,3 В | 12 В | 12 В |

Узел питания C1 (POWER)

Принципиальная схема этого узла изображена на рис. 26.

Телевизоры на шасси LC13E питаются от внешнего источника (сетевого адаптера) напряжением 12 В (13" и 15") или 24 В (20").

Гнездо 1101-1 (см. рис. 26), в которое включается сетевой адаптер, расположено в узле C1 (POWER). Через предохранитель 1002 на 7 А напряжение 12/24 В поступает на ключи включения рабочего режима 7003 и 7005 узла С1, а через разъемы 1003 С1 и 1902 А10 (рис. 27) на ключ 7900 и микросхему 7920 типа MC34063A.

В дежурном режиме ключ на транзисторе 7003 закрыт, а в рабочем он открывается высоким уровнем сигнала STAND-BY от МК. На коллекторе 7003 будет низкий потенциал, которым включается стабилизатор напряжения 5 В 7001 типа LM2596T-5.0. Из этого напряжения с помощью микросхемы 7009 типа LD1086V33 формируется напряжение 3,3 В, а из него формируется напряжение 1,8 В стабилизатором на микросхеме 7006 типа LD1086D2T18.

В узле С1 предусмотрена защита, блокирующая микросхему 7001 типа LM2596T-5.0 при завышенном напряжении питания. Схема защиты состоит из порогового устройства на стабилитроне 6001 (15В для телевизоров 13", 15" и 27 В для аппаратов 20") и ключа на транзисторе 7002.

Из этой таблицы видно, что цепи, формирующие напряжения питания разных LCD-панелей, должны заметно отличаться. Во всех этих цепях для включения питания LCD-панелей используется ключ на полевом транзисторе 7005, который управляется биполярным транзистором 7004, а он - командой PANEL-PWR-CTL с узла.

В телевизорах с диагональю экрана 13" установлены стабилизатор 3,3 В на микросхеме 7011 типа LD1117DT33 и дроссель 5010 и не установлены дроссели 5011, 5013, 5014 и элементы, обведенные пунктирной линией. Значит, при отпирании ключа 7005 на стабилизатор 7011 поступит напряжение 5 В от стабилизатора 7001. Напряжение 3,3 В с выхода стабилизатора 7011 будет использоваться как напряжение питания LCD-панели LC130V01.

В телевизорах с диагональю экрана 15" установлены дроссели 5011, 5013 и не установлены дроссели 5010, 5014, микросхема стабилизатора 7011 и элементы, обведенные пунктирной линией. В этом случае, при отпирании ключа 7005, через этот ключ и дроссели 5011, 5013 напряжение 12 В от сетевого адаптера поступит в цепи питания LCD-панели LC150X01.

В телевизорах с диагональю экрана 20" установлены дроссели 5011,5014 и элементы,обведенные пунктирной линией. Дроссели 5010, 5013 и микросхема стабилизатора 7011 не установлены. Элементы, обведенные пунктирной линией - это стабилизатор 12 В на микросхеме 7010 типа MC34063A. При отпирании ключа 7005 на вход этого стабилизатора от сетевого адаптера через дроссели 5011 и 5015 поступит напряжение 24 В, а напряжение с выхода стабилизатора 12 В через дроссель 5014 поступит в цепи питания LCD-панели LC201V02.

Узел питания платы TV A10 (LOCAL SUPPLY)

Принципиальная схема этого узла показана на рис. 27.

Полевой транзистор 7900 используется в качестве силового ключа, обеспечивающего включение рабочего режима. Им управляет цифровой транзистор 7901.

В рабочем режиме высокий логический уровень команды STAND-BY от МК открывает 7901, а тот, в свою очередь, открывает 7900. Напряжение питания 12/24 В через ключ 7900, предохранитель 1903 (1,6 А) и дроссель 5930 поступает на стабилизаторы 8,3 В (микросхема 7910 MC34063A) и 5,4 В (7930 MC34063A).

Микросхема 7920 MC34063A используется в качестве стабилизатора напряжения 3,5 В для питания микроконтроллера как в рабочем, так и в дежурном режимах.

В узел A10 входит схема защиты телевизора при значительном уменьшении напряжения питания (от сетевого адаптера), которая собрана на транзисторах 7903 и 7904. Низкий логический уровень на коллекторе 7904 (сигнал POWER-DOWN) поступает на МК (в цепи баз транзисторов 7067, 7068) и узел УМЗЧ A9 (на выв. 2, 9 и 12 микросхемы 7732 74LCV08AD) для блокировки работы аппарата.

Все недостающие схемы и рисунки можно найти здесь.

Литература

1. Безверхний. И. LCD-панели LC130V01, LC150X01 и LC201V02 производства LG.PHILIPS LCD Co., Ltd для телевизионных приемников. "Ремонт & Сервис", №9, 2006.

2. Безверхний И. Импульсные блоки питания DVD-проигрывателя DVDQ50 фирмы Philips. "Ремонт & Сервис", № 1, 2006.

3. Безверхний. И. Инверторы для LCD панелей LC130V01, LC150X01 и LC201V02. "Ремонт & Сервис", № 12, 2006.

4. В. Петров. Устройство и ремонт инверторов для ЖК мониторов. "Ремонт & Сервис", № 3, № 4, 2005.

5. Безверхний И. MSP3410D - многостандартный процессор звука для современных аналоговых и цифровых телевизоров. Chip News. 2004. № 1, с. 24-31.

6. MICRONAS. PRELIMINARY DATA SHEET. MSP 3400D, MSP 3410D Multistandard Sound Processors. Edition May 14, 1999 (6251-482-2PD).

Автор: Игорь Безверхний (г. Киев)

Источник: Ремонт и сервис