Стремительное развитие микропроцессорной техники привело к повсеместному внедрению микроконтроллеров, управляющих различными устройствами. В ближайшем будущем встретить устройство без микроконтроллера будет всё сложнее. Миниатюризация и повышенная производительность микроконтроллеров позволяют значительно расширить функциональные возможности устройств. Современное развитие технологии приводит к логическому появлению такого явления, как Интернет вещей (IoT), но для его реализации необходимо иметь мощное ядро и развитую периферию микроконтроллера, когда в одной микросхеме реализовано всё будущее устройство. Инженеру остаётся только написать программу, реализующую алгоритм его работы. Семейство процессорных ядер Cortex-M как раз и предназначено для этого.

Начиная обзор, вернёмся в 1990 г., когда несколько компаний решили организовать совместное предприятие Advanced RISC Machines Ltd. (ARM). Это были Apple Computer, Arcon Computer Group и VLSI Technology. В 1991 г. было представлено первое ядро этой компании. Оно получило название ARM6, а компания VLSI первой получила лицензию на его производство. Потом и другие компании последовали её примеру и приобрели лицензии. В числе этих компаний были такие гиганты, как Texas Instruments, NEC, Sharp, STMicroelectronics. Это привело к повсеместному применению ядра ARM6 в разнообразной технике - КПК, мобильных телефонах, жёстких дисках и разнообразной бытовой технике.

Компания ARM сама не производит и не продаёт процессоры на основе собственных разработок. Она лишь занимается разработкой и лицензированием процессорных ядер, которые реализуют в кремниевых кристаллах другие компании. ARM предлагает различные условия лицензирования, различающиеся стоимостью и конечными результатами. Всем лицензиатам ARM предоставляет интегрируемое аппаратное описание ядра ARM, полный набор инструментов для разработки программного обеспечения и право на продажу изготовленных кристаллов, содержащих процессор ARM.

Производители интегрированных устройств (IDM) получают ядро процессора ARM как интеллектуальную собственность, синтезируемый модуль RTL, написанный на Verilog. Это позволяет выполнить оптимизацию архитектуры ядра и расширять его в зависимости от назначения. Всё это позволяет реализовать нестандартные конструкции, например, с увеличенной тактовой частотой, уменьшенным энергопотреблением или совместить ядро с каким-либо датчиком.

Для повышения плотности кода начиная с 1994 г, когда было создано ядро ARM7TDMI, были введены дополнительные 16-разрядные команды, позволяющие оптимизировать программу по размеру используемого кода. Этот набор, названный Thumb, состоит из 36 команд, преобразованных из стандартных 32-разрядных команд ARM в 16-разрядные. Они имеют меньшую функциональность и фактически ограничивают использование 32-разрядного ядра на полную мощность. Напрямую можно обращаться только к восьми младшим регистрам общего назначения, с восемью старшими можно делать лишь несколько операций. Отсутствует умножение с накоплением/расширением, сопроцессорные операции, доступ к PSR и регистрам других контекстов, атомарный обмен SWAP и т. д.

Для устранения этих недочётов, выявленных в наборе команд Thumb, был создан модифицированный набор команд, получивший название Thumb-2. Впервые он был представлен в 2003 г. в ядре ARM1156. В нём устранены ограничения 16-разрядного набора Thumb путём расширения его 32-разрядными командами, что привело к переменной длине команд. Эти команды предназначены для повышения производительности ядра с одновременным уменьшением места, занимаемого в памяти. Старый набор команд Thumb был расширен операциями с битовыми полями, командами ветвления и условного выполнения.

Компания ARM представила на рынок семейство Cortex-M в 2004 г., когда было анонсировано первое ядро этого семейства Cortex-M3. В 2007 г. она представила ядро Cortex-M1, в 2009 г. - Cortex-M0, в 2010 г. - Cortex-M4, в 2012 г. - Cortex-M0+, в 2014 г. - Cortex-M7, в 2016 г. - Cortex-M23 и Cortex-M33.

Ядро Cortex-M предназначено для использования в микроконтроллерах, процессорах, ПЛИС, специализированных продуктах и системах на кристалле (SOC). На заре компьютерной эры были широко распространены восьмиразрядные микроконтроллеры, но техника и технология не стоят на месте, и теперь им на смену приходят 32-разрядные микроконтроллеры (как-то так получилось, что 16-разрядные микроконтроллеры не завоевали умы разработчиков, как восьмиразрядные).

Одно из них - семейство процессорных ядер семейства Cortex-M, позволяющее при той же цене получить наибольшую вычислительную мощность за счёт использования 32-разрядного ядра. Ядра этого семейства компания ARM позиционирует следующим образом:

- Cortex-M0, Cortex-M0+ и Cortex-M23 предназначены для приложений, требующих минимальных стоимости, энергопотребления и размеров кристалла;

- Cortex-M3, Cortex-M4 и Cortex-M33 предназначены для приложений, в которых производительность 32-разрядного ядра сбалансирована с энергопотреблением;

- Cortex-M7 используется для встраиваемых приложений, требующих высокой производительности.

В ядра Cortex-M23 и Cortex-M33 включена технология ARM TrustZone, обеспечивающая комплексную безопасность приложений. Cortex-M4, Cortex-M7 и Cortex-M33 могут иметь, кроме того, интегрированный процессор цифровой обработки сигналов (DSP), дающий возможность выполнять арифметические операции с плавающей запятой, что позволяет применять алгоритмы цифровой обработки сигналов различных датчиков. Это даёт возможность, например, более эффективно управлять асинхронным двигателем.

Теперь можно более подробно рассмотреть семейство Cortex-M.

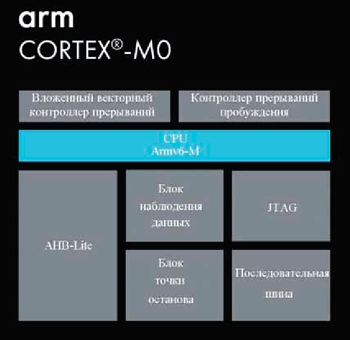

Ядро Cortex-M0 (рис. 1) имеет кристалл небольшой площади, низкое энергопотребление, для него нужен код минимального размера. Процессор позволяет разработчикам достичь высокой производительности, характерной для 32-разрядного ядра.

Рис. 1. Ядро Cortex-M0

Ультранизкое число используемых вентилей даёт возможность применять это ядро в устройствах, использующих аналоговую или смешанную обработку сигналов. Энергопотребление ядра M0, в зависимости от исполнения и решаемых задач, колеблется от 4 до 73 мВт/МГц. Скорость его работы - 0,84 DMIPS/МГц. Разработчики попытались получить законченное процессорное ядро. Поэтому в его состав включены все необходимые для этого элементы: контроллер прерывании на 32 вектора, интерфейс периферийных устройств в виде 32-разрядной шины AsB-Lite, отладчик. При необходимости процессор может оснащаться контроллером "спящего" режима.

Основные особенности:

- архитектура ARMv6-M;

- набор инструкций Thumb/Thumb-2;

- трёхуровневый конвейер;

- битовые манипуляции;

- одно немаскируемое прерывание и от 1-го до 32-х физических прерываний;

- аппаратное одноцикловое умножение 32x32 разряда;

- в зависимости от производителя может быть доступен 24-разрядный таймер SysTick;

- для перехода в спящий режим имеются инструкции WFI или WFE;

- отладка возможна через JtAg или SWD.

Это ядро используют, например, микроконтроллеры Cypress PSoC 4, Cypress PSoC 4M, Cypress PSoC 4L; Infineon XMC1000; Nordic nRF51; NXP LPC1100, LPC1200; семейство nuvoTon NuMicro M0 Family; Sonix SN32F700; STMicroelectronics STM32F0; Toshiba TX00; Vorago VA10800 (экстремальная температура), VA10820 (радиационностойкие).

Кроме этого, есть микроконтроллеры с двумя ядрами, одно из которых - Cortex-M0. Так фирма NXP создала микроконтроллер LPC4300 (одно ядро Cortex-M4F и одно Cortex-M0), фирма Texas Instruments - микроконтроллеры CC1310 и CC2650 (одно ядро Cortex-M3, одно Cortex-M0 и специальный процессор для датчика контроля двигателя).

Отечественные разработчики (ПКК "Миландр") тоже не отстают от зарубежных фирм и запустили в производство микроконтроллер 1986ВЕ4У1. Он работает на тактовой частоте до 36 МГц, содержит 128 Кбайт FLASH-памяти программ и 16 Кбайт ОЗУ. При этом имеет интервал рабочей температуры от -60 до +125 оС. Кроме того, разработаны микроконтроллеры К1986ВК234 и К1986ВК214 для трёхфазного счётчика электроэнергии.

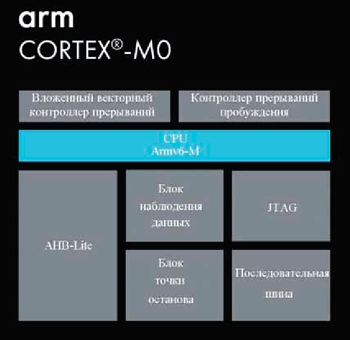

Cortex-M0+ (рис. 2) - дальнейшее развитие ядра Cortex-M0 с целью снижения энергопотребления (3 мВт/МГц, что меньше, чем у младшего ядра семейства Cortex-M0) и повышения производительности до 0,94 DMIPS/МГц. Оно содержит одноцикловую систему ввода/вывода для ускоренного управления, микробуфер трассировки (MTB), используемый для отладки, и другие общие для семейства Cortex-M элементы, например блок защиты памяти (MPU).

Рис. 2. Ядро Cortex-M0+

Основные особенности Cortex-M0+:

- архитектура ARMv6-M;

- набор инструкций Thumb/Thumb-2;

- двухуровневый конвейер;

- защита памяти (8 регионов);

- одно немаскируемое прерывание и от 1-го до 32-х физических прерываний;

- для перехода в спящий режим имеются команды WFI и WFE;

- аппаратное одноцикловое умножение 32x32 разряда;

- отладка возможна через JTAG или SWD;

- дополнительно может присутствовать микробуфер трассировки (MTB).

Это ядро используют микроконтроллеры Atmel SAMD, SAMR, SAML, SAMC; Cypress PSoC 4S,FM0+;Holtek HT32F52xxx; NXP LPC800, LPC11 E6x, LPC11U6x; Freescale Kinetis E, EA, L, M, V1, W0; Renesas Synergy S1; Silicon Labs EFM32 Zero, Happy; STMicroelectronics STM32L0.

Ядро Cortex-M1 разработано специально для реализации в микросхемах FPGA. Его основные особенности:

- архитектура ARMv6-M;

- набор инструкций: Thumb/Thumb-2;

- трёхуровневый конвейер;

- аппаратный умножитель 32x32 разряда с 32-разрядным результатом;

- одно немаскируемое прерывание и от 1-го до 32-х физических прерываний;

- дополнительно может быть реализована сильно связанная память (TCM) объёмом от 0 до 1 Мбайт для команд и от 0 до 1 Мбайт для данных;

- отладка может отсутствовать, быть упрощённой или полной;

- порядок следования данных little-endian или BE-8 big-endian;

- поддержка операционной системы может присутствовать или нет.

Это ядро можно использовать, например, в FPGA Altera Cyclone-II, Cyclone-III, Stratix-II, Stratix-III; Microsemi (Actel) Fusion, IGLOO/e, ProASIC3L, ProASIC3/E; Xilinx Spartan-3, Virtex-2, Virtex-3, Virtex-4.

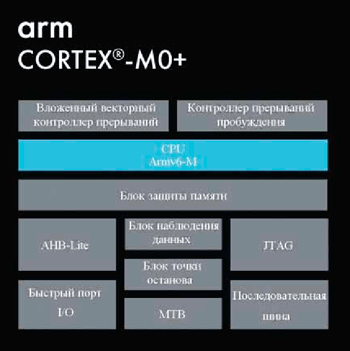

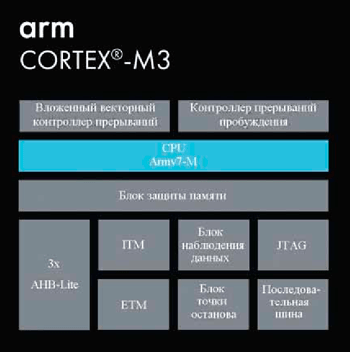

Рис. 3. Ядро Cortex-M3

Cortex-M3 (рис. 3) - наиболее популярное у производителей и разработчиков микроконтроллеров ядро с архитектурой aRm. Это самое первое появившееся на рынке ядро семейства Cortex-M. Оно основано на архитектуре ARMv7-M и полностью реализует наборы команд Thumb и Thumb2. Производительность - 1,25 DMIPS/МГц. Энергопотребление примерно в два раза больше, чем у Cortex-M0. Основные особенности ядра Cortex-M3:

- гарвардская архитектура Armv7-M;

- набор инструкций Thumb/Thumb-2;

- трёхуровневый конвейер;

- защита памяти от 0 до 8 регионов;

- аппаратный умножитель 32x32 разряда с 32- или 64-разрядным результатом, знаковым или беззнаковым, со сложением или вычитанием после умножения;

- одно немаскируемое прерывание и от 1-го до 240 физических прерываний;

- от 8 до 256 уровней приоритетов прерываний;

- контроллер до 240 прерываний;

- для перехода в спящий режим имеются команды WFI и WFE;

- манипуляция битами;

- контроллер прямого доступа к памяти (DMA);

- аппаратное деление (от 2 до 12 циклов);

- отладка через JTAG или SWD, имеется возможность трассировки отлаживаемого кода.

Это ядро используют, например, микроконтроллеры Actel SmartFusion, SmartFusion 2; Analog Devices ADuCM3xx; Atmel SAM3A, SAM3N, SAM3S, SAM3U, SAM3X; Cypress PSoC 5, 5LP, FM3; Holtek HT32F; NXP LPC1300, LPC1700, LPC1800; ON Semiconductor Q32M210; Realtek RTL8710; Silicon Labs Precision32, EFM32 Tiny, Gecko, Leopard, Giant; STMicroelectronics STM32F1, F2, L1, W; Texas Instruments F28, LM3, TMS470, OMAP 4, CC1310, CC2650; Toshiba TX03.

Отечественные разработки - микроконтроллеры 1986ВЕ92У, 1986ВЕ93У, K1986BE92QI, 1986ВЕ94Т, 1986ВЕ91Т.

Некоторые компании используют Cortex-M3 как второе ядро. В Apple A9 это интегрированный сопроцессор движения M9, в CSR Quatro 5300 - сопроцессор, в Samsung Exynos 7420 - DVS микроконтроллер, в Texas Instruments F28, LM3, TMS470, OMAP 4470 содержится одно ядро Cortex-A9 и два ядра Cortex-M3, в MOS XS1-XA - семь ядер xCORE и одно ядро Cortex-M3. Компания Microsemi встроила ядро Cortex-M3 в свою FPGA SmartFusion2.

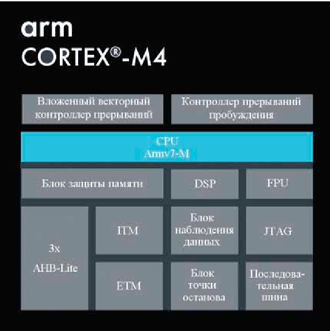

Ядро Cortex-M4 (рис. 4) разработано для управления устройствами, в которых необходима цифровая обработка сигнала. Можно считать, что это улучшенный вариант ядра Cortex-M3, оснащённый дополнительным модулем цифрового сигнального процессора (DSP). Производительность у него такая же, как и у Cortex-M3 - 1,25 DMIPS/МГц. Сочетает высокую эффективность обработки сигналов с низким энергопотреблением, невысокой ценой и простотой в использовании. В серии M4 есть ещё один вариант под обозначением Cortex-M4F. В нём дополнительно к DSP установлен блок операций над числами с плавающей запятой (FPU).

Рис. 4. Ядро Cortex-M4

Основные особенности ядра Cortex-M4:

- гарвардская архитектура Armv7E-M;

- набор инструкций Thumb/Thumb-2;

- трёхуровневый конвейер c предсказанием ветвлений;

- команды цифровой обработки. Одноцикловые 16/32-разрядные MAC (умножение с накоплением), одноцикловые двойные 16-разрядные MAC, 8/16-разрядные SIMD (одна команда - много данных), аппаратное деление (от 2 до 12 циклов);

- аппаратный умножитель 32x32 разряда с 32- или 64-разрядным результатом, знаковым или беззнаковым, со сложением или вычитанием после умножения;

- по желанию дополнительно может быть поставлен блок обработки чисел с плавающей запятой одинарной точности, совместимый с IEEE 754, называемый FPv4-SP расширением;

- защита памяти от 0 до 8 регионов;

- одно немаскируемое прерывание и от 1-го до 240 физических прерываний;

- от 8 до 256 уровней приоритетов прерываний;

- для перехода в спящий режим имеются команды WFI и WFE;

- битовая манипуляция;

- отладка через JTAG или SWD, имеется возможность трассировки отлаживаемого кода.

Примеры микроконтроллеров, использующих ядро Cortex-M4: Analog Devices CM4xx Mixed-Signal Control Processors; Atmel SAM4L, SAM4N, SAM4S; Freescale Kinetis K, W2; Texas Instruments CC3200 и CC3200MOD.

Примеры микроконтроллеров, использующих ядро Cortex-M4F: Atmel SAM4C (два ядра), SAM4E, SAMG, SAM E5x, SAM D5x; Cypress PSoC6, FM4; Infineon XMC4000; Microchip CEC1302; Nordic nRF52; NXP LPC4000, LPC4300 (одно ядро Cortex-M4F и одно Cortex-M0); Freescale Kinetis K, V3, V4; Renesas Synergy S3, S5, S7; Silicon Labs EFM32 Wonder; STMicroelectronics STM32 F3, F4, L4; Texas Instruments LM4F, TM4C, MSP432; Toshiba TX04; отечественная разработка 1986ВЕ8Т.

Примеры микроконтроллеров, использующих Cortex-M4 как второе ядро: Freescale Vybrid VF6 (одно ядро Cortex-A5 и одно Cortex-M4F); Freescale i.MX 6 SoloX (одно ядро Cortex-A9 и одно Cortex-M4F); Freescale i.MX 7 Solo/Dual (одно или два ядра Cortex-A7 и одно Cortex-M4F); Texas Instruments OMAP 5 (два ядра Cortex-A15s, два Cortex-M4); Texas Instruments Sitara AM57xx (одно или два ядра Cortex-A15s и два Cortex-M4s как модуль обработки изображений и два ядра Cortex-M4s блока общего назначения).

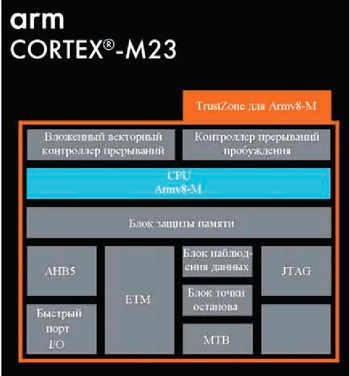

Cortex-M23 (рис. 5) - это относительно новое ядро на основе архитектуры Дж. фон Неймана Armv8-M, представленное в 2016 г. Идейно это ядро похоже на Cortex-M0+ с дополнительными функциями безопасности TrustZone. Ядро Cortex-M23 имеет двухуровневый конвейер, поддерживающий базовый набор команд Armv8-M. Он предназначен для приложений, где ключевое требование - безопасность. TrustZone для Armv8-M обеспечивает аппаратную принудительную изоляцию между доверенными и ненадёжными ресурсами устройства Cortex-M23, сохраняя при этом эффективную обработку исключений и детерминизм (переход из основной задачи на обработку прерывания за минимально возможное и, самое главное, определённое заранее время). Это было отличительной чертой всех процессоров с ядром Cortex-M.

Рис. 5. Ядро Cortex-M23

В совокупности с низким энергопотреблением доверенное выполнение даже на самых маленьких, маломощных и ограниченных по возможностям встроенных устройствах обеспечивает безопасность IoT

Основные особенности ядра Cortex-M23:

- архитектура Дж. фон Неймана Armv8-M;

- набор инструкций Thumb/Thumb-2;

- двухуровневый конвейер;

- технология защиты TrustZone;

- дополнительно может быть оснащён блоком защиты памяти (MPU) на 0, 4, 8, 12 или 16 регионов;

- дополнительно может быть поставлен блок задания атрибутов безо-

пасности (SAU) на 0, 4 или 8 регионов;

- одно немаскируемое прерывание и до 240 физических прерываний с четырьмя уровнями приоритетов;

- аппаратное одноцикловое умножение и деление 32x32 разряда;

- отладка через JTAG или SWD;

- дополнительно может быть поставлен микробуфер трассировки (MTB) или встраиваемая макроячейка трассировки (ETM).

Микроконтроллер Nuvoton M2351 остаётся пока единственным с ядром Cortex-M23, хотя другие производители активно работают в этом направлении.

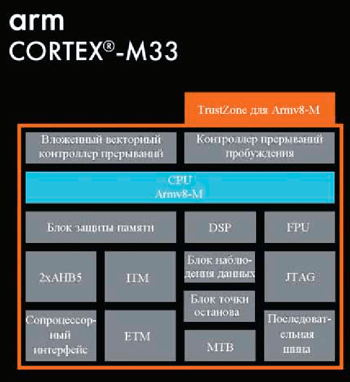

Ядро Cortex-M33 (рис. 6) также было представлено в 2016 г. Оно основано на той же архитектуре, что и Cortex-M23. Но идейно оно похоже на ядро Cortex-M4, что позволяет сочетать повышенную производительность (приблизительно на 20 % больше, чем у ядер Cortex-M3 и Cortex-M4) с обеспечением безопасности приложений. TrustZone для Armv8-M обеспечивает безопасность, а дополнительные узлы, такие как DSP, интерфейс сопроцессора, блок защиты памяти и блок плавающей запятой, значительно расширяют сферу его применения.

Рис. 6. Ядро Cortex-M33

Основные особенности ядра Cortex-M33:

- архитектура Дж. фон Неймана Armv8-M;

- набор инструкций Thumb/Thumb-2;

- трёхуровневый конвейер;

- технология защиты TrustZone;

- аппаратный целочисленный 32разрядный делитель;

- регистр ограничения стека;

- дополнительные DSP/SIMD команды, одноцикловые 16/32-разрядные MAC, одноцикловые двойные 16-разрядные MAC, 8/16-разрядная SIMD арифметика;

- блок FPU одинарной точности с плавающей запятой, совместимый с IEEE 754;

- дополнительно может быть поставлен блок защиты памяти (MPU) на 0, 4, 8, 12 или 16 регионов;

- дополнительно может быть поставлен блок задания атрибутов безопасности (SAU) на 0, 4 или 8 регионов;

- немаскируемые прерывания и до 480 физических прерываний от 8 до 256 уровней приоритета;

- отладка через JTAG или SWD;

- дополнительно может быть поставлены микробуфер трассировки (MTB) или встраиваемая макроячейка трассировки (ETM), трассировка данных (DWT) и инструментальная трассировка (ITM).

Примером использования ядра Cortex-M33 может быть микроконтроллер Nordic nRF91, вероятно, и другие производители в ближайшем будущем выпустят свои варианты данного ядра.

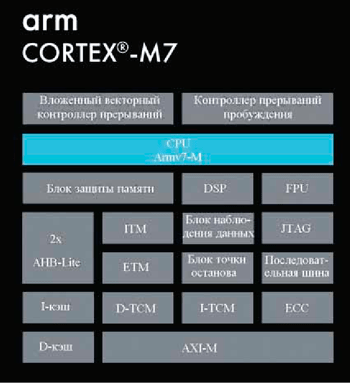

Ядро Cortex-M7 (рис. 7) - самое сложное из семейства Cortex-M. Оно позволяет создавать самые совершенные микроконтроллеры и системы на кристалле (SOC). По сравнению с предыдущими вариантами изменена ширина шины данных и команд с 32 до 64 разрядов, что позволило значительно повысить производительность ядра. Ядро Cortex-M7 основано на простой и лёгкой в использовании архитектуре Armv7-M, позволяя использовать его в самых разных отраслях - автомобильной и другой промышленности, обработке аудио- и медиаданных, Интернете вещей (IoT).

Рис. 7. Ядро Cortex-M7

Основные особенности этого ядра:

- гарвардская архитектура Armv7-M;

- шестиуровневый суперскалярный конвейер с предсказанием ветвлений;

- набор инструкций Thumb/Thumb-2;

- одноцикловые 16/32-разрядные

команды MAC, одноцикловые двойные 16-разрядные команды MAC, 8/16-разрядная SIMD арифметика, аппаратное 32-разрядное деление занимает от 2 до 12 циклов;

- аппаратный умножитель 32x32 разряда с 32- или 64-разрядным результатом, знаковым или беззнаковым сложением или вычитанием после умножения;

- 64-разрядная AMBA4 AXI, AHB шина;

- немаскируемые прерывания и от 1-го до 240 физических прерываний,

имеющих от 8 до 256 уровней приоритета;

- отладка с интегрированными командами через JTAG или SWD.

Дополнительно может быть использовано следующее:

- блок обработки чисел с плавающей запятой одинарной и двойной точности, совместимый с IEEE 754 и называемый FPv5 расширением;

- кэш инструкций объёмом от 0 до 64 Кбайт с двухуровневой ассоциативной ECC;

- кэш данных объёмом от 0 до 64 Кбайт с четырёхуровневой ассоциативной ECC;

- инструкции TCM от 0 до 16 Мбайт с ECC;

- данные TCM от 0 до 16 Мб с ECC;

- защита памяти на 8 или 16 зон;

- микробуфер трассировки (MTB) или встраиваемую макроячейку трассировки (ETM), трассировку данных (DWT) и инструментальную трассировку (ITM).

Примеры микроконтроллеров, использующих ядро Cortex-M7: Atmel SAME70, SAMS70, SAMV70; Freescale Kinetis KV5xi.MX RT; STMicroelectronics STM32F7, STM32H7.

Автор: А. Николаев, г. Боготол Красноярского края