Основные характеристики и конструктивные особенности

Телевизионное шасси Q522.2E LA (платформа TV522/22E*) является производным от ТВ шасси Q522.1E LA (платформа TV522/22M), которое, в свою очередь, является упрощенной версией ТВ шасси Q528.2E (платформа TV522/82M, основное отличие - модуль Ambilight). Все эти шасси являются преемниками ТВ шасси предыдущего поколения BJ3.0 и BJ3.1. На рассматриваемом шасси в 2008 году выпускались следующие модели c диагоналями ЖК панелей от 32 до 47 дюймов: 32PFL5403, 32PFL5403D, 32PFL5403S, 37PFL3403D, 37PFL5603, 37PFL5603D, 37PFL5603S, 42PFL5603D, 42PFL5603S, 47PFL5603D. Все эти модели поддерживают фирменную технологию улучшения HD-изображения Pixel Plus HD. Основные технические характеристики телевизоров приведены в таблице 1.

Таблица 1. Основные технические характеристики телевизоров

Спецификация | Модель | |||

32PFL5403/xx* | 37PFL5603/xx | 42PFL5603/xx | 47PFL5603/xx | |

Диагональ ЖК панели, дюймы | 32 | 37 | 42 | 47 |

Тип подсветки ЖК панели | Краевая CCFL (EEFL)-подсветка | |||

Физическое разрешение панели, пикселы (HxV) | 1366x768 | 1920x1080 | ||

Углы обзора | 176x176 | |||

Яркость, кд/м2 | 500 | |||

Интерфейс ЖК панели | LVDS | LVDS (2-канальный) | ||

Время отклика матрицы, мс | 5 | |||

Диапазон контрастности | 24000:1 | 30000:1 | ||

ТВ системы | ||||

РЧ вход | PAL (B/G, D/K, I), SECAM (L/L', B/G , D/K), DVB COFDM 2K/8K | |||

Входы CVBS/S-video | PAL, NTSC и SECAM | |||

Тип тюнера и диапазоны | PLL (цифровой синтез частоты). UHF, VHF, S, Hyper | |||

Поддерживаемые форматы и типы файлов | ||||

Видеоформаты | 480i/p@60 Гц, 576i/p@50 Гц, 720p@50/60 Гц, 1080i@50/60 Гц, 1080p@25/30/50/60 Гц | |||

Компьютерные форматы | 1024x768, 800x600, 640x480 | |||

Типы файлов | JPEG, MP3, Slideshow (.alb) | |||

Телетекст | Память на 1200 страниц | |||

Другие характеристики | ||||

Звуковая мощность, Вт | 2 х 15 Вт | |||

Питание (АС) | 220...240 В, 50/60±2 Гц | 90.264 В, 50/60±3 Гц | ||

Входы USB | USB 2.0 | |||

Потребляемая мощность максимальная/в дежурном режиме, Вт | 130/0,15 | 170/0,15 | 200/0,15 | 260/0,15 |

* XX - код страны-производителя | ||||

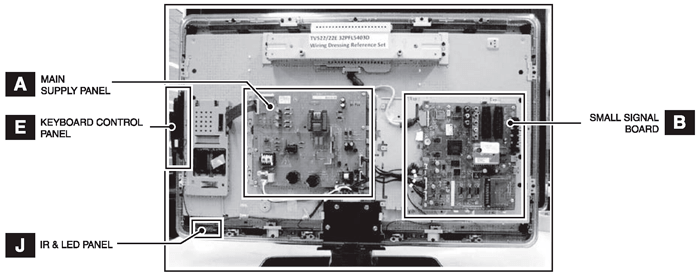

Конструктивно ТВ шасси Q522.2E LA включает в себя следующие платы:

- плата малых сигналов SSB;

- плата локальной панели управления IR & LED;

- плата индикации и фотоприемника IR & LED;

- плата блока питания SUPPLY PANEL.

Телевизоры выпускаются в двух исполнениях (дизайн корпуса) - ME8 (32-, 42- и 47-дюймовые модели) и MG8 (37-дюймовая модель). В пластмассовом корпусе на подставке размещены ЖК панель, закрытая металлическим кожухом (экраном), а на нем установлены указанные выше платы. В качестве примера на рис. 1 приведен внешний вид 32-дюймовой модели с открытой задней крышкой.

Рис. 1. Внешний вид 32-дюймовой модели с открытой задней крышкой

Блок-схема шасси

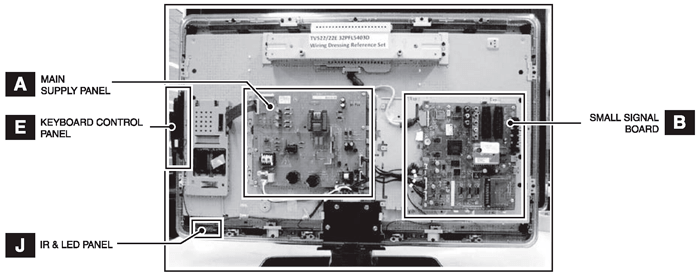

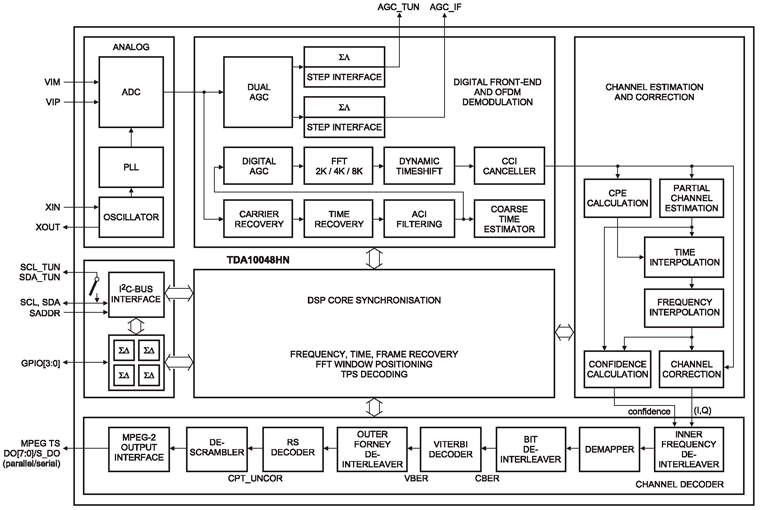

Блок-схема архитектуры ТВ шасси Q522.2E LA приведена на рис. 2.

Рис. 2. Блок-схема архитектуры ТВ шасси Q522.2E LA

Основой шасси является многофункциональная ИМС PNX8541 фирмы NXP Микросхема выполнена по технологии SoC (System on a Chip - система на кристалле) и фактически она обеспечивает все функциональные возможности телевизора (см. характеристики в таблице 1). Внутренняя архитектура ИМС PNX8541 частично приведена на блок-схемах трактов обработки аудио- и видеосигналов (см. рис. 3 и 5 (см. архив ниже)).

ТВ сигнал с антенны поступает на вход гибридного тюнера1T04 (рис. 3). Тюнер управляется по цифровой шине I2C ИМС PNX8541, напряжение настройки VTUN для него формируется этой же ИМС.

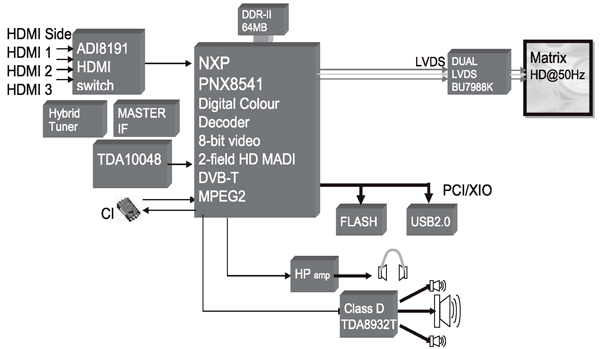

На выходе тюнера формируется дифференциальный сигнал 1-й ПЧ (выходы IF1, IF2), который через соответствующий полосовой фильтр на ПАВ 1T56 или 1T70, формирующие АЧХ видеотракта, поступает на процессор ПЧ 7T57 типа TDA9898. ИМС является мульти-стандартным процессором ПЧ как аналогового (ATV), так и цифрового ТВ (DTV), включая стандарты L и L', а также FM-радио. В зависимости от принимаемого стандарта на выходе ПЧ процессора формируется композитный ПЦТС или дифференциальный сигнал 2-й ПЧ, которые поступают на блок аналоговой обработки в составе ИМС PNX8541 (ANALOGUE AV на рис. 3) или на цифровой приемник 7T17 типа TDA10048. Архитектура этой ИМС приведена на рис. 4.

Рис. 4. Архитектура ИМС TDA10048

По интерфейсу I2C ИМС настраивается на несущую частоту требуемого ТВ канала и переносит входной сигнал на нулевую ПЧ, выделяя из него I- и Q-составляющие. Затем эти сигналы декодируются в сигнал транспортного потока TS, сжатый в стандарте MPEG2, и с выхода ИМС в параллельном коде поступает на вход декодера MPEG2 в составе ИМС PNX8541. Этот же вход используется для подключения разъема PCMCIA, который используется для установки SMART-карты с целью приема кодированных каналов или для подключения устройств с интерфейсом PCMCIA.

Если используется один из аналоговых входов ТВ (компонентный вход YPBPR, разъемы SCART, S-video, Jack), то сигнал с этого входа также поступает на блок аналоговой обработки ИМС PNX8541.

Рассматриваемое шасси обеспечивает подключение до 4-х DVI-устройств через разъемы HDMI. Дифференциальные пары сигналов с этих разъемов поступают на ИМС переключателя 7P70 (рис. 3), затем выбранный пользователем сигнал с его выхода подается на вход HDMI.

Вся последующая обработка видеосигналов, аналоговых или цифровых, выполняется ИМС PNX8541. Для хранения промежуточных данных PNX8541 использует динамическую память DDR2 - два банка с архитектурой 8Мх16х4 общим объемом 64 Мбит. Управляющие программы хранятся во Flash-памяти NAND объемом 512 Мбайт В результате обработки на выходе ИМС PNX8541 формируется цифровой LVDS-сигнал - 6 пар дифференциальных сигналов (включая тактовый сигнал) TX8OA(B, C, D, CLK)+, TX8OA(B, C, D, CLK)-, которые через интерфейсный разъем 1G50 поступают на ЖК панель. Этот 1-канальный интерфейс используется с панелями HD Ready 32 и 37 дюймов с физическим разрешением 1366х768 пикселей. Для управления панелями Full HD c диагоналями 42 и 47 дюймов (1920х1080 пикселей) используется 2-канальный интерфейс LVDS - дополнительный 2-й канал формируется из цифровых TTL-сигналов на выходе PNX8541 VIDEO OUT TTL. Сигналы подаются на LVDS-передатчик 7CG0 и с его выхода через интерфейсный разъем 1G50 сигналы TX8EA(B, C, D, CLK)+, TX8EA(B, C, D, CLK)- поступают на ЖК панель.

Блок-схема тракта обработки аудиосигналов приведена на рис. 5. Как и в предыдущем случае, практически вся обработка звукового сигнала происходит в ИМС PNX8541. Из эфирного сигнала ПЧ в аналоговом тракте ИМС выделяется звуковой сигнал и поступает на коммутатор аналоговых сигналов звука. Сюда же подаются аналоговые звуковые сигналы с разъемов SCART, JACK, DVI, компонентного и S-video. Выбранный пользователем сигнал (вход) оцифровывается и подается на цифровой звуковой процессор в составе ИМС PNX8541. После соответствующей обработки цифровой сигнал звука поступает на оптический выход (узел B07B на рис. 5) и на выходной ЦАП (узел В04L). Отсюда аналоговые стереосигналы звука поступают на внешний цифровой уси-

литель мощности 7D10, а с его выходов - на динамические головки.

Сигнал для усилителя наушников 7HV3 формируется отдельным ЦАП в составе PNX8541.

ИМС PNX8541 имеет три интерфейса I2C. По одному из них ИМС соединена с микросхемами приемного тракта: ПЧ процессором 7N57, цифровым ресивером 7Е17 и, через эту ИМС, с гибридным тюнером 1Т04. Второй и третий интерфейсы I2C служат для связи главного микропроцессора MIPS (Microprocessor without Interlocked Pipeline Stages) в составе PNX8541 c дежурным встроенным и с ИМС главной энергонезависимой памяти 7НС3.

У дежурного MIPS-контроллера имеется последовательный интерфейс UART (RXD, TXD), линии которого выведены на сервисные разъемы 1E05 и 1Е50. Он используется в заводских условиях для сервисных регулировок (запись-чтение сервисных данных).

В составе узла цифрового входа PNX8541 также имеется интерфейс I2C DDC (Display Data Channel). Через мультиплексор 7P70 он подключается к соответствующей ИМС энергонезависимой памяти (в зависимости от используемого входа HDMI1-HDMI3) для считывания параметров подключенного внешнего устройства.

В узле LVDS-интерфейса DUAL LVDS в составе PNX8541 также имеются две линии, запрограммированные как интерфейс UART. По этому интерфейсу ИМС управляет LVDS-передатчиком 7СG0.

Для детального ознакомления со схемотехникой шасси можно обратиться к его принципиальной электрической схеме, основные узлы которой приведены на вкладке.

Система питания шасси будет достаточно подробно рассмотрена в одном из следующих номеров журнала.

Блок-схема тракта обработки видеосигналов и блок-схема тракта обработки аудиосигналов находятся здесь.

Продолжение следует

Автор: Леонид Ларионов (г. Ахтубинск)

Источник: Ремонт и сервис