В предыдущей статье автора [1] были рассмотрены домашние кинотеатры (ДК) Philips HTS-5131, усилительные тракты которых выполнены на основе технологии PureParth™ компании Texas Instruments. Эта технология применяется и в ряде других моделей ДК PHILIPS (HTS-5220, 3538, 3551, 5533), в которых используется комплект микросхем TAS5508/TAS5342A (или TAS5352A).

Построение моделей HTS-5110/12/51/98, HTS-5120/12/51/55/78/93/98 (разработка 2010 года, внешний вид на рис. 1) существенно отличается как по структуре, так и по элементной базе. В аппаратах реализована технология AC Dolby Virtual на основе двухканальной "звуковой панели" (SoundBar), устанавливаемой под телевизором, и беспроводного сабвуфера. Длина основного блока соответствует длине ЖК телевизоров с диагональю 32 дюйма. Объемное звучание класса 5.1 формируется двумя плоскими фронтальными акустическими системами (по 3 динамика в каждой), встроенными в низкопрофильный основной блок(габариты 790 х 144 х 57,4 мм), и звуковым процессором с обработкой Dolby Pro Logic II, преобразующим стереосигналы в псевдомногоканаль-ные. При монтаже этих домашних кинотеатров не требуются провода для подключения колонок, сеть переменного тока подключается к сабвуферу и сетевому адаптеру SRP846/01 (аналог G721DA-2700250, см. рис. 2), соединенному с основным блоком. Сетевой адаптер представляет собой импульсный преобразователь напряжения с выходным напряжением 27 В и обеспечивает ток в нагрузке до 2,5 А.

Рис. 1. Внешний вид ДК HTS-5110//5120

Рис. 2. Сетевой адаптер G721DA-2700250

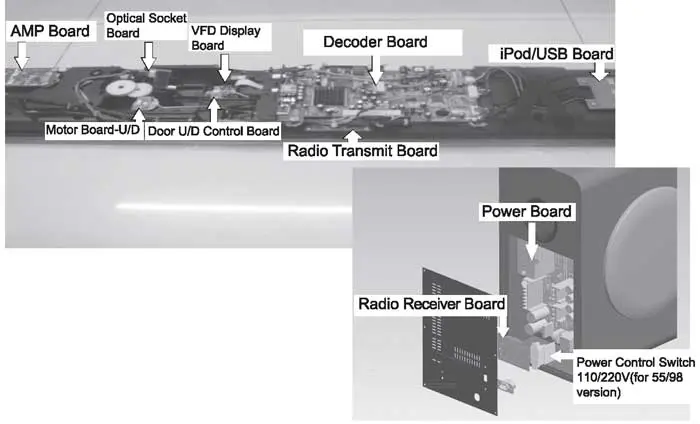

В состав основного блока ДК входят следующие узлы и платы: главная плата (Decoder Board), плата дисплея (VFD Display Board), плата УМЗЧ (AMP Board), механизм привода дисков (Loader Driver Mechanism), платы входов выходов (Optical Socket Board, iPod/USB/MP3 Link Board), плата кнопок управления (Touch Board), плата передатчика системы беспроводной связи с сабвуфером.

В состав сабвуфера входят силовая плата (Power Board) и плата приемника системы беспроводной связи. Структурная схема и схема соединений ДК HTS-5120 приведены ниже в архиве, а расположение узлов и плат - на рис. 3. Отличия модели HTS-5110: нет проигрывателя дисков (только внешние источники); нет отдельной платы УМЗЧ (входит в состав главной платы); отсутствуют платы оптических входов и подключения iPod.

Рис. 3. Расположение узлов и плат в корпусе ДК HTS-5120

Рис. 4. Структура микросхемы AP1501-5V

Главная плата основного блока (Decoder Board)

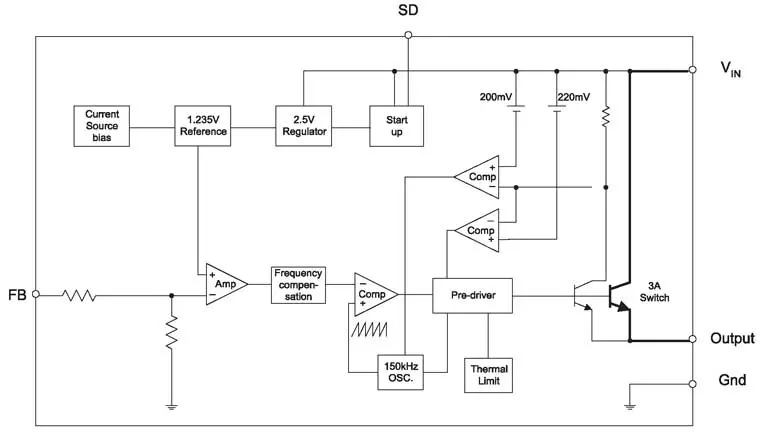

Первичное напряжение питания +27 В поступает на основной блок от внешнего сетевого адаптера, принципиальная электрическая схема источника питания основных блоков ДК HTS-5110 и HTS-5120 приведена в архиве (см. ниже). Первичное напряжения по цепи 27V_IN поступает на вход понижающего импульсного преобразователя напряжения, выполненного на микросхеме U1 AP1501-5V фирмы Anachip (Тайвань, в настоящее время поглощена компанией Diodes Ink), формирующего напряжение +5 В (цепь DC5V). Микросхемы АР1501 выпускаются в нескольких исполнениях по выходному напряжению (3,3, 5 и 12 В и с регулируемым выходом) и в различных корпусах (T0220-5L, TO263-5L, цоколевки совпадают), структура микросхемы приведена на рис. 4, основные особенности и параметры микросхем:

- частота коммутации (методом ШИМ): 150 кГц;

- эффективность (КПД): 73 % (UВЫХ = 3,3 В), 80 % (5 В), 90 % (12 В);

- минимальное входное напряжение: 4,5...12 В (при UВЫХ = 1,23...12 В);

- максимальное входное напряжение:40 В;

- максимальный выходной ток 3 А (порог срабатывания защиты 3,6...5,5 А).

Напряжение с выхода микросхемы U1 поступает на коммутируемый каскад, выполненный на транзисторах U2 и Q1. Сборка из p-канального полевого транзистора и обратного диода U2 APM9435K фирмы ANPEC, выполнена в корпусе SO-8 и характеризуется низким значением RDS ON = 50...80 мОм при выходном токе 2...4,6 А. Основные параметры сборки: UСИ МАКС= 30 В, РРАСС=2,5 Вт, заряд затвора Qg=22,5 нк, СВХ=845 пФ.

Напряжение +3,3 В (цепи DVD3.3V, 89S_3V3, DV33, RFV33) обеспечивает стабилизатор с малым падением напряжения U3 CX1084-3,3 фирмы Silicon Core Microelectronics. Микросхема характеризуется следующими параметрами: UВХ = 4,75...12 В, IВЫХ=5 А, нестабильность выходного напряжения при изменении выходного тока в пределах 0,01...5 А - не более 25 мВ. В серии СХ1084 имеются и другие исполнения микросхем на выходные напряжения 1,5, 2,5, 2,85, 3, 3,3, 3,5 В и с регулируемым выходным напряжением (CX1084-ADJ).

Напряжение +1,8 В (цепь V18) обеспечивает регулируемый стабилизатор напряжения U4 CX1117-ADJ также фирмы Silicon Core. В серии СХ1117 предусмотрены исполнения с фиксированными выходными напряжениями 1,5, 1,8, 2,5, 2,85, 3,3 и 5 В, другие параметры микросхем: IВЫХМАКС = 1,5 А, UВХ МИН = 1,5...6,5 В (в зависимости от исполнения), UВХ МАКС = 12 В.

Сигнал включения коммутируемого каскада MPEGON поступает на базу транзистора Q1 с выв. 3 микроконтроллера системы управления U16 R5R0C028FA компании Renesas (см. схему системы управления обеих рассматриваемых моделей ДК в архиве), ПО ДК хранится в ЭСППЗУ U16 24C02. Напряжение питания +3,3 В микроконтроллера обеспечивает стабилизатор напряжения U26 на вышеописанной микросхеме CX1117-3,3 (цепь 3.3 V MCU).

При проведении диагностики неисправностей ИП следует обращать внимание на целостность дросселей выходных фильтров.

Декодер видео- и звуковых сигналов проигрывателя дисков и сигналов, поступающих с внешних источников, выполнен на микросхеме MT1389S фирмы MediaTek. Принципиальная электрическая схема декодера модели HTS5120 приведена в архиве (см. ниже), поскольку в модели HTS5110 нет проигрывателя дисков, схема декодера в ней упрощена в адресной части (также используется микросхема MT1389S). Медиапроцессоры серии МТ1389 широко применяются во множестве DVD-плееров различных производителей, исполнение MT1389S является одним из первых комплексных решений, прошедших сертификацию Microsoft. БИС представляет собой систему на кристалле (СнК), обеспечивающую расширенные функции, в том числе обработку сигналов формата Windows Media Video 9 (WMV9) и всех профилей кодека VC-1, а также обработку сигналов высокой четкости и преобразования форматов стандартной четкости в HD (до 1080i/p). Другие особенности БИС:

- поддержка интерфейсов HDMI, USB 2.0 и карт-ридеров;

- поддержка форматов MPEG2/4, DiVX/DiVX Ultra, HD-JPEG, SACD, DVD-Audio;

- видео ЦАП 148 МГц/12 разрядов;

- технология адаптивной компенсации движения при преобразовании чересстрочной развертки в прогрессивную (MDDiTM).

В БИС интегрирован 8-канальный звуковой ЦАП (192 кГц/24 разряда), обеспечивающий высококачественное воспроизведение звука с дисков и внешних цифровых входов, в связи с чем микросхема нашла применение в продукции известных аудиофильских компаний (Marantz, Yamaha, TEAC и др.), например DVD-проигрыватель "Marantz DV4003" на основе MT1389S обеспечивает THD=0,003% (Total Harmonic Distortion - относительный общий коэффициент искажений) и отношение "сигнал/шум" 110 дБ.

Рис. 5. Структура микросхемы UDA1355H

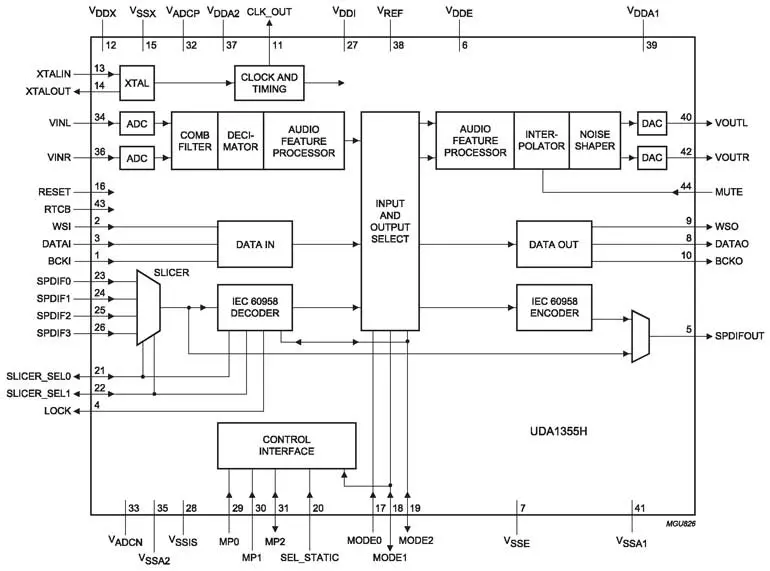

Преобразование внешних аналоговых сигналов и сигналов УКВ тюнера в цифровую форму (формат I2S)обеспечивает микросхема U15 UDA1355H компании NXP, соответствующая принципиальная электрическая схема части главной платы модели HTS5120 приведена на в архиве (см. ниже). Микросхема выполнена в корпусе QFP44 и представляет собой стереоаудиокодек с интерфейсом SPDIF. Структура микросхемы приведена на рис. 5. Особенности и параметры микросхемы:

- АЦП с 24-разрядным цифровым интерполирующим фильтром;

- усилитель с программируемым коэффициентом усиления (Programmable Gain Amplifier - PGA);

- 24-разрядный ЦАП, не требующий применения аналоговых постфильтров;

- форматы выходных сигналов - I2S, с левым и правым выраниванием (LSB/MSB-justified) в 16/18/20/24-разрядном представлении;

- 3-проводной и I2C интерфейсы управления;

- частоты дискретизации АЦП от 16 до 100 кГц;

- цифровая регулировка громкости в пределах -63,5...+24 дБ с шагом 0,5 дБ;

- частоты дискретизации ЦАП 32; 44,1; 48; 96 кГц.

- относительный общий коэффициент искажений с шумом ЦАП (THD +N/S) - -88 дБ;

- отношение сигнал/шум (S/N) - 98 дБ.

Рис. 6. Структурная схема применения 4-канального аудиопроцессора PT2313H

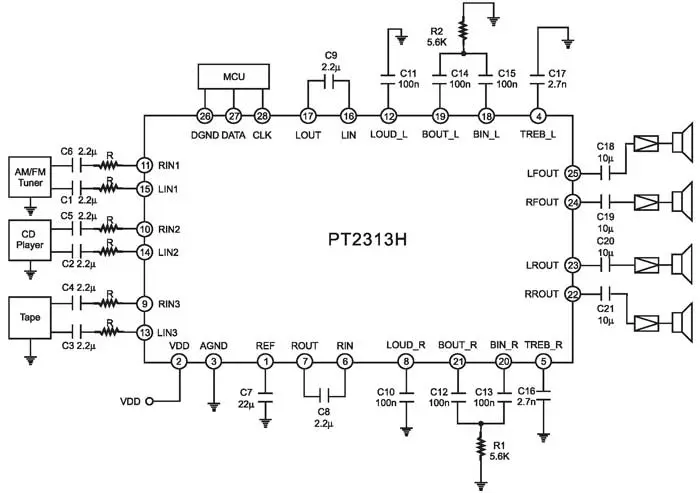

Обработку выходных сигналов БИС MT1389S обеспечивает 4-канальный аудиопроцессор U17 PT2313 (см. рис. 6) фирмы Princeton Technology Corp. (Тайвань), обеспечивающий преобразование двух стереоканалов в 4 канала объемного звука. В рассматриваемых ДК источниками сигналов для этой микросхемы являются декодер проигрывателя дисков (цепи AR1, AL1), УКВ тюнер (FM IN L1, FM IN R1) и док-станция iPod (iPod INL, iPod INR). Звуковые сигналы с выходов левого и правого фронтальных каналов микросхемы поступают на УМЗЧ ДК (выв. 24, 25), выходы левого и правого тыловых каналов (выв. 23, 22) суммируются и поступают на процессор низкочастотного канала, выполненного на микросхеме U21 MX3000/NC. Основные особенности и параметры микросхемы РТ2313:

- независимая регулировка громкости каждого канала с шагом 1,25 дБ;

- регулировка тембра по НЧ и ВЧ;

- входы/выходы (выв. 6, 7, 16, 17) для подключения внешних эквалайзеров с обеспечением совместимости с микросхемой 5-полосного эквалайзера TDA7313 (в рассматриваемых ДК не используется);

- управление по шине I2C.

В рассматриваемых домашних кинотеатрах не используется технология цифровых усилителей PureParthTM, а высокое качество звуковоспроизведения обеспечивается за счет отличных параметров ЦАП, интегрированного в БИС MT1389S. УМЗЧ обеих моделей ДК выполнены по одинаковой схеме, приведенной на вкладке (в модели HTS-5120 УМЗЧ выполнен на отдельной плате AMP BOARD). В состав УМЗЧ входят активный двухзвенный фильтр верхних частот, выполненный на сдвоенных ОУ U23, U25 CF4558. В качестве усилителей мощности применены микросхемы U22, U24 TPA3123D2 компании Texas Instruments. Микросхема TPA3123D2, выполнена в корпусе TSSOP-24 и представляет собой 2-канальный усилитель звуковых частот класса D с аналоговыми входами мощностью 25 Вт на канал.

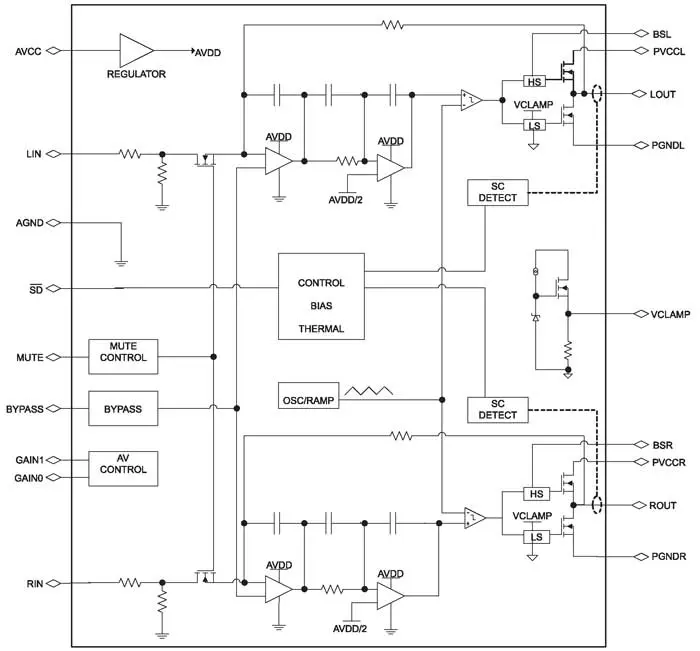

Рис. 7. Структура микросхемы TPA3123D2

Структура микросхемы приведена на рис. 7, в ее состав входят: генератор треугольного напряжения (OSC/RAMP), подключенный к инвертирующим входам компараторов напряжения левого и правого каналов; двухкаскадные усилители-формирователи импульсов левого и правого каналов,нагруженные на ключи верхнего и нижнего плеч (HS/LS), выполненные на мощных полевых транзисторах; схемы управления, смещения и регулировки усиления (MUTE CONTROL, BYPASS, AV CONTROL); схемы защиты и детекторы коротких замыканий (CONTROL, BIAS, THERMAL, SC DETECT), стабилизатор напряжения (REGULATOR). В микросхеме реализована ШИМ типа AD (см. [1]), основные особенности и параметры микросхемы:

- изменяемый коэффициент усиления 20/26/32/36 дБ;

- внутренний генератортреу-гольного напряжения частотой 230...270 кГц без внешних компонентов;

- несимметричные аналоговые входы;

- совместимость по выводам с микросхемой TPA3120D2;

- высокоэффективный класс D без необходимости применения теплоотводов;

- схемы защиты от перегрева и коротких замыканий с автовосстановлением;

- отсутствие щелчков при включении питания;

- напряжение питания 10...30 В;

- выходная мощность каждого канала в однотактном режиме SE при THD+N=1 % - 16 Вт (RН = 4 Ом, UПИТ = 24 В), 8 Вт (RН = 8 Ом, UПИТ = 24 В);

- суммарный коэффициент искажений с шумом (THD+N) - 0,008 % (РВЫХ = 10/5 Вт, UПИТ = 4/8 Ом, f=1 кГц);

- отношение "сигнал/шум" - 99 дБ (КУ=20 дБ, THD+N менее 1 %).

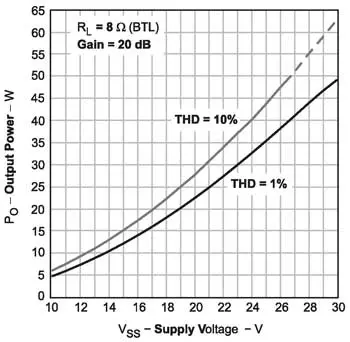

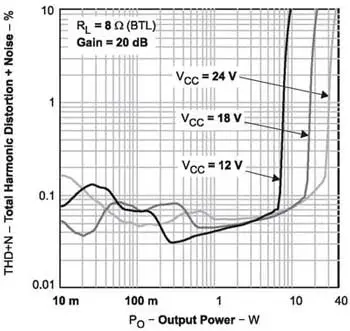

В рассматриваемых ДК два канала микросхемы используются в мостовом режиме BTL, зависимости выходной мощности УМ в этом режиме от напряжения питания при различном уровне искажений приведены на рис. 8. Зависимость THD от выходной мощности при различных напряжениях питания приведены на рис. 9.

Рис. 8. Зависимость выходной мощности УМ в режиме BTL от напряжения питания при различном уровне искажений

Рис. 9. Зависимость THD от выходной мощности УМ при различных напряжениях питания

Сабвуфер

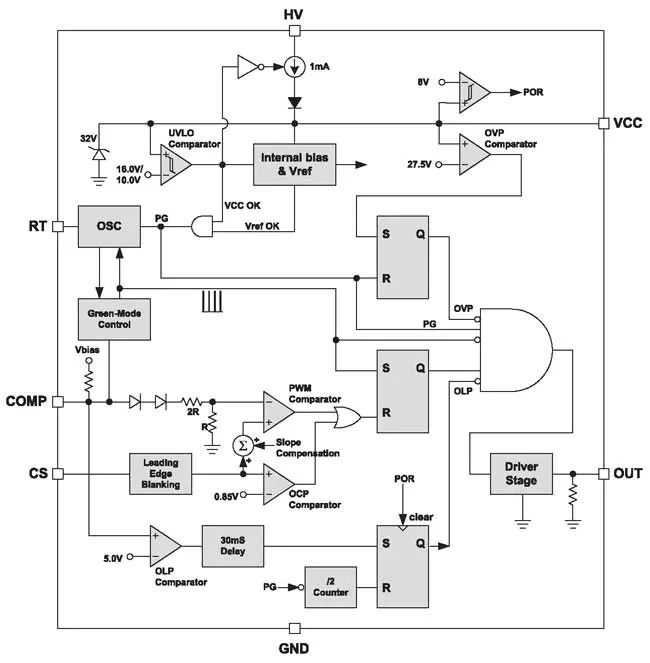

В состав сабвуфера ДК входит плата беспроводного приемника (Radio Receiver Board) и силовая плата (Power Board), на которой выполнены источник питания и усилитель мощности НЧ канала. Принципиальная электрическая схема источника питания приведена на вкладке. Первичная часть ИП представляет собой обратноходовый преобразователь напряжения на основе ШИМ контроллера IC1 LD7550 фирмы Leadtrend Technology Corporation (Тайвань) и оптрона IC2 типа EL817. При работе от сети напряжением 220 В используются все компоненты фильтра основного выпрямителя на диодах D1-D4, для работы от сети напряжением 100...120 В контакты разъема CON4 соединяются перемычкой, при этом в составе фильтра остаются только элементы R5, CE1, MOV1. Структура ШИМ контроллера LD7575 приведена на рис. 10, основные особенности и параметры микросхемы:

Рис. 10. Структура ШИМ контроллера LD7575

- схема высоковольтного запуска (до 500 В);

- беззвучная работа источника питания (без писка);

- блокировка при низком напряжении питания (UVLO);

- подавление выбросов на фронтах импульсов (Leading-Edge Blacking);

- регулируемая частота коммутации;

- компенсация наклона плоской вершины импульсов (Slope Compensation);

- схемы защиты от перегрузки по току (OLP) и перенапряжений (OVP);

- выходной ток до 500 мА Назначение выводов микросхемы (корпуса SOP-8, DIP-8) приведено в таблице.

Таблица. Назначение выводов микросхемы LD7575

Номер вывода | Обозначение | Назначение |

1 | RT | Вывод для подключения резистора установки частоты переключения, частота определяется формулой fпрекл=65/Rt (кОм) х 100 (кГц), при Rt =100 кОм частота 65 кГц. При малых нагрузках и на холостом ходу ИП микросхема переходит в экономичный режим (Green-Mode Operation) с частотой коммутации 20 кГц |

2 | СОМР | Вход обратной связи (подключается к фототранзистору оптрона) |

3 | CS | Вход для подключения датчика тока (резистора) в цепи истока мощного полевого транзистора ИП |

4 | GND | Первичный корпус |

5 | OUT | Выход драйвера на затвор полевого транзистора ИП |

6 | VCC | Напряжение питания 11...25 В (поступает с выпрямителя, подключенного к отдельной обмотке ИТ) |

8 | HV | Вход запуска, при снижении напряжения на выводе VCC ниже допустимого значения цепь запуска блокируется |

Выход микросхемы (выв. 5) может нагружаться непосредственно на затвор мощного ключевого MOSFET, однако в ИП сабвуферов рассматриваемых ДК применен промежуточный каскад на комплементарных транзисторах Q2, Q3 типа 8050/8550 (выпускаются различными производителями), основные параметры транзисторов: UKЭ = ±25 В, IК = 1,5 (-0,5) А, h21э = 85-300, fТ=150 МГц. В качестве Q1 можно применять практически любые MOSFET c параметрами IC=10 A, UСИ=600 В.

ИП обеспечивает вторичные напряжения +27 В (цепь +Vo), -27 B (-Vo) с выпрямителей D9, D12 и +5 В с линейного стабилизатора напряжения на транзисторах Q4, Q5.

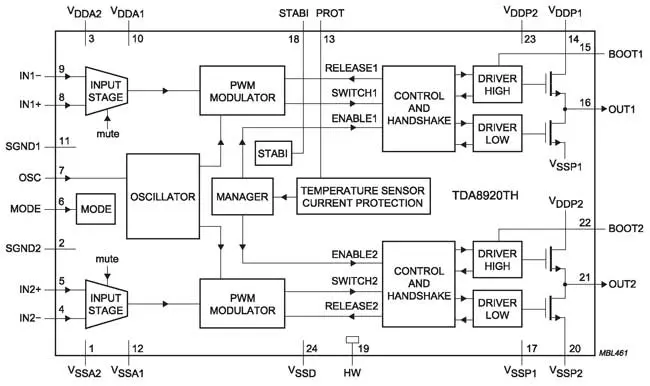

Принципиальная электрическая схема УМЗЧ сабвуфера приведена в архиве (см. ниже). Он базируется на микросхеме IC6 TDA8920CJ фирмы NXP - двухканальном УЗЧ класса D с аналоговыми входами. Структура микросхемы приведена на рис. 11. Особенности этой и других микросхем - усилителей класса D компании NXP - приведены в статье автора [2].

Рис. 11. Структура микросхемы TDA8920CJ

Беспроводную связь сабвуфера с основным блоком обеспечивают цифровые приемопередатчики, установленные на плате передатчика основного блока (Radio Transmitter Board) и плате приемника сабвуфера (Radio Receiver Board). Для установления связи требуется идентифицировать конкретные приборы, для чего инициируется режим установки двусторонней связи кнопками на основном блоке и сабвуфере, обеспечивающий их синхронную работу (Pair Operation). После чего приемопередачик основного блока работает преимущественно в режиме передачи, а приемопередатчик сабвуфера - в режиме приема.

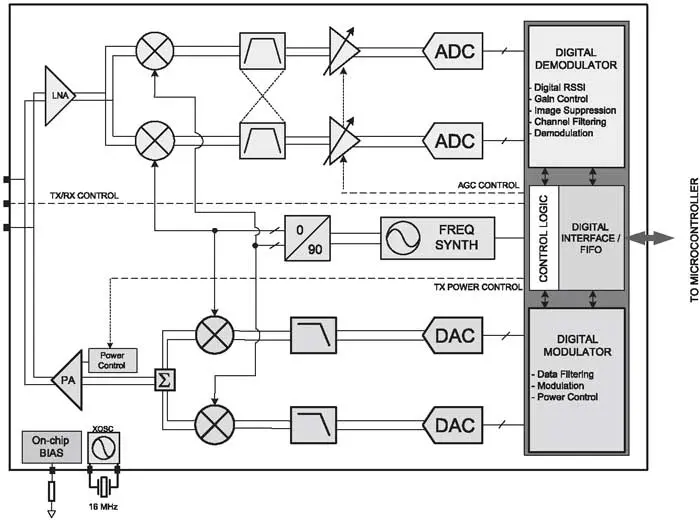

Рис. 12. Структура микросхемы СС2400

Принципиальная электрическая ВЧ части сабвуфера приведена на вкладке, ВЧ часть основного блока выполнена практически по такой же схеме. В качестве трансиверов использованы однокристальные БИС диапазона ISM (2,4 ГГц) СС2400 фирмы Texas Instruments (позиция U3). Микросхема выполнена в корпусе QLP48 и представляет собой ВЧ трансивер с низким энергопотреблением. БИС обеспечивает полную поддержку операций с пакетами данных, что значительно разгружает управляющий контроллер, в качестве которого можно использовать недорогие микроконтроллеры с невысокой производительностью. Структура микросхемы приведена на рис. 12, в состав приемника входят: ВЧ МШУ (LNA), смесители, полосовые фильтры, регулируемые усилители, АЦП и цифровой демодулятор. В состав передатчика входят цифровой модулятор, ЦАП, ФНЧ, сумматор, регулируемый аттенюатор и ВЧ усилитель (РА). Общими узлами являются синтезатор частоты гетеродина (FREQ SYNTH), фазовращатель (0/90 °), кварцевый генератор (16 МГц), схема питания, управляющая логика и цифровой интерфейс управления (Digital Interface/FIFO). Основные особенности и параметры микросхемы:

- рабочий диапазон частот: 2400...2483,5 МГц;

- тип модуляции: FSK (Frequency Shift Keing) - частотная манипуляция, GFSK (Gaussian Frequency Shift Keying) - частотная манипуляция с ограниченным спектром (используется фильтр Гаусса);

- программируемая скорость передачи: 10 кбит/с, 250 кбит/с, 1 Мбит/с;

- чувствительность приемника: -87 дБм /1 Мбит/с, поток ошибок BER=10-3;

- быстрая перестройка частоты (время установки частоты 40 мкс);

- программируемая выходная мощность: -25 дБм...0 дБм);

- напряжение питания: 1,6...3,6 В (интерфейс), 1,6...2 В (ядро);

- ток потребления 25 мА в режиме приема;

- аппаратная поддержка операций с пакетами, буферизация данных (32 байта FIFO).

Принципиальная электрическая схема управления приемопередатчика сабвуфера приведена в архиве (см. ниже), в ее состав входят микропроцессор U1 HMX6026E1 (производитель не идентифицирован), ЭСППЗУ U6 FM24C02B и управляющий 8-разрядный микроконтроллер U10 EM78P153SN фирмы ELAN Microelectronics (Тайвань).

В схеме управления приемопередатчика основного блока используется тот же микропроцессор HMX6026E1, а управляющий микроконтроллер отсутствует.

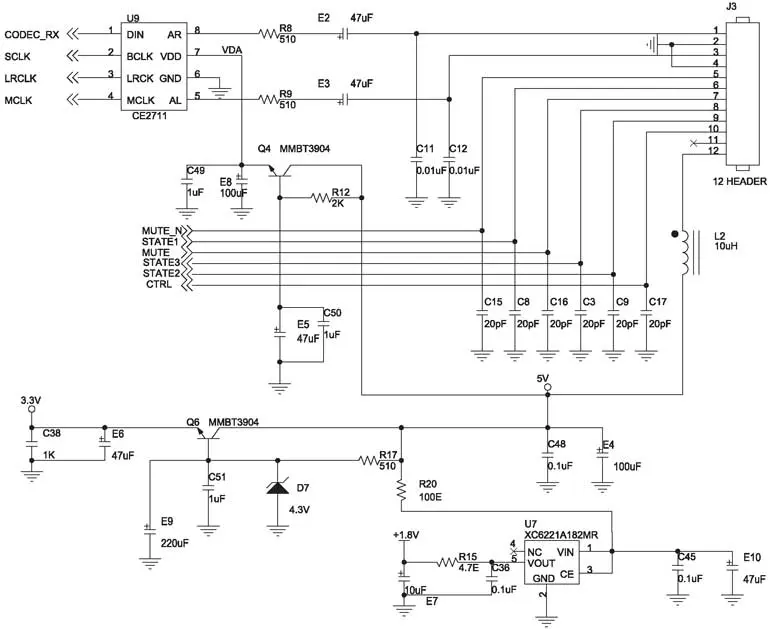

Принципиальная электрическая схема стабилизаторов напряжения и фильтров приемопередатчика сабвуфера приведена на рис.13. В схему также включен ЦАП U9 CE2711 фирмы CEI Microelectronics (КНР), предназначенный для преобразования цифровых звуковых сигналов формата I2S в аналоговые сигналы. В соответствующей схеме приемопередатчика основного блока используется АЦП CE2732 той же фирмы, предназначенный для обратной задачи.

Рис. 13. Принципиальная электрическая схема стабилизаторов напряжения и фильтров приемопередатчика сабвуфера

Схемы, упомянуте в статье можно скачать здесь.

Литература и интернет-источники

1. Юрий Петропавловский, "Технология цифровых усилителей PureParth™ в домашних кинотеатрах Philips HTS-3538/3551/5131/ 5200/5220/5233. Устройство и ремонт домашнего кинотеатра HTS5131", Ремонт & Сервис, 2013, № 9.

2. Юрий Петропавловский, "Особенности и параметры микросхем для импульсных усилителей звуковых частот компании NXP", Радиолоцман, октябрь 2011.

3. http://www.rlocman.ru/book/ book.html?di=111722

Юрий Петропавловский (г. Таганрог)

Источник: Ремонт и сервис