В цифровых многоканальных системах дистанционного пропорционального управления моделями [1-3] сигналы, содержащие информацию об угловом положении исполнительного органа сервоприводов, формируются изменением ширины канальных импульсов, вырабатываемых шифратором команд передатчика, длительность которых, в зависимости от положения рукояток управления передатчика, может изменяться в интервале 1...2 мс. Для передачи информации по каналу связи эти импульсы преобразуются в синхроимпульсы фиксированной длительности 0,1...0,5 мс, образующие канальные посылки, разделённые синхропаузой, и следующие с частотой 50...60 Гц. Информация о передаваемом значении команды в соответствующем канале управления содержится во временном интервале между синхроимпульсами канальной посылки, а число импульсов в ней зависит от числа каналов управления.

Дешифратор команд приёмника распределяет импульсы этой последовательности по каналам управления, восстанавливает ширину канальных импульсов и передаёт их на соответствующие сервоприводы. Как правило, для дешифрации команд используются счётчики-распределители канальных импульсов, работающие по следующему циклу: каждый поступающий синхроимпульс канальной посылки дешифрируемого сигнала изменяет состояние счётчика-распределителя канальных импульсов, которое сохраняется до прихода следующего синхроимпульса, а после прохождения всей последовательности синхроимпульсов канальной посылки счётчик-распределитель канальных импульсов возвращается в исходное состояние сформированным дешифратором команд импульсом обнуления.

Недостаток этих дешифраторов команд - низкая помехозащищённость, поскольку при воздействии импульсных помех, источником которых могут быть, например, сигналы посторонних передатчиков, а также установленные на модели электродвигатели, регуляторы напряжения дискретного действия, электромагнитные реле и другие подобные устройства, не исключена возможность нарушения этими помехами цикла работы счётчика-распределителя канальных импульсов и формирование вследствие этого дешифратором команд ложных сигналов управления сервоприводами модели, результат исполнения которых, как правило, - авария модели. Особенно подвергнут воздействию импульсных помех дешифратор команд во время формирования передатчиком синхропаузы, когда на вход дешифратора команд синхроимпульсы не поступают [1].

Предлагаю свободный от указанного недостатка свой вариант дешифратора команд для многоканальной системы дистанционного пропорционального управления моделями. Он предназначен для работы с шифратором команд, описанным в [4], но может быть использован и с другими аналогичными устройствами. Техническое решение, положенное в основу этого дешифратора команд, защищено патентом Российской Федерации на изобретение [5].

Основные технические характеристики

Число дешифрируемых каналов ................. 4

Входное сопротивление, кОм, не менее .................5

Амплитуда синхроимпульсов на входе, В, не менее .................1

Амплитуда канальных импульсов на выходе, В, не менее .................4

Напряжение питания, В .................5

Ток потребления, мА, не более .................5

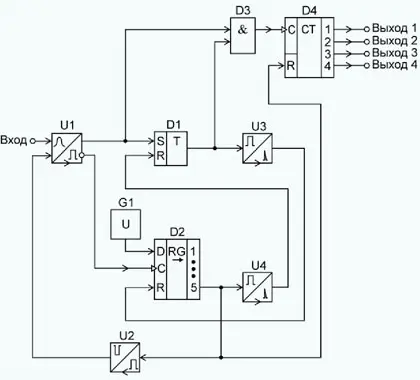

Рис. 1. Функциональная схема дешифратора команд

Функциональная схема дешифратора команд представлена на рис. 1, где D1 - RS-триггер; D2 - сдвиговый регистр; D3 - логический элемент 2И; D4 - счётчик-распределитель канальных импульсов; G1 - формирователь напряжения высокого логического уровня; U1 - пороговое устройство; U2 - формирователь прямоугольных импульсов напряжения фиксированной длительности; U3, U4 - формирователи коротких импульсов напряжения.

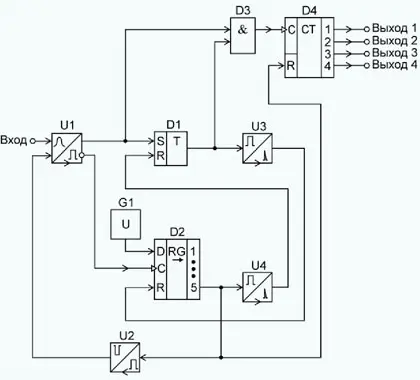

На рис. 2 приведены временные диаграммы импульсных напряжений в характерных точках дешифратора команд, поясняющие его работу (для наглядности масштаб по осям абсцисс и ординат не соблюдён).

Рис. 2. Временные диаграммы импульсных напряжений в характерных точках дешифратора команд

Дешифратор команд работает так. В четырёхканальной системе дистанционного пропорционального управления на вход дешифратора команд с выхода приёмника поступает последовательность из пяти искажённых шумами синхроимпульсов канальной посылки Uвх. При превышении этими синхроимпульсами порогового напряжения Uпорог, установленного выше максимального уровня шумовых выбросов, пороговое устройство U1 в моменты времени t1, t2, t3, t4, t5 формирует на своём прямом и инверсном выходах фронт прямоугольных импульсов напряжения Uвых.1ПУ и спад противофазных импульсов напряжения Uвых.2ПУ соответственно, при этом длительность импульсов напряжения Uвых.1ПУ определяется длительностью синхроимпульсов канальной посылки, а длительность импульсов напряжения Uвых.2ПУ - длительностью временного интервала между спадом и фронтом смежных синхроимпульсов этой канальной посылки.

В момент времени t1 с прямого выхода порогового устройства U1 на вход S установки в единичное состояние RS-триггера D1 поступает импульс напряжения Uвых.1ПУ высокого логического уровня, в результате чего на выходе RS-триггера D1 формируется напряжение Uвых.Т высокого логического уровня. Это напряжение подаётся на один из входов логического элемента 2И D3, а также на вход формирователя коротких импульсов U3.

В момент времени t1 формирователь коротких импульсов U3 формирует на своём выходе кратковременный перепад напряжения Uвых.ФКИ1 с низкого на высокий логический уровень. Этот перепад напряжения поступает на вход установки в нулевое состояние сдвигового регистра D2, при этом во всех его разрядах формируется напряжение Uвых.РС низкого логического уровня.

Поскольку в этот момент логический элемент 2И D3 открыт напряжением Uвых.Т высокого логического уровня, на выход этого логического элемента проходят импульсы напряжения Uвых.1ПУ, которые поступают на тактовый вход счётчика-распределителя канальных импульсов D4.

Счётчик-распределитель канальных импульсов D4 восстанавливает ширину канальных импульсов и распределяет их по соответствующим выходам дешифратора команд телеуправления: в момент времени t1 на первом выходе счётчика-распределителя канальных импульсов D4 формируется напряжение Uвых.1 высокого логического уровня, а в момент времени t2 - низкого логического уровня; в момент времени t2 на втором выходе счётчика-распределителя канальных импульсов D4 формируется напряжение Uвых.2 высокого логического уровня, а в момент времени t3 - низкого логического уровня; в момент времени t3 на третьем выходе счётчика-распределителя канальных импульсов D4 формируется напряжение Uвых.3 высокого логического уровня, а в момент времени t4 - низкого логического уровня; в момент времени t4 на четвёртом выходе счётчика-распределителя канальных импульсов D4 формируется напряжение Uвых.4 высокого логического уровня, а в момент времени t5 - низкого логического уровня.

Одновременно с этим на тактовый вход C сдвигового регистра D2 с инверсного выхода порогового устройства U1 поступают импульсы напряжения Uвых.2ПУ. Поскольку на информационный вход D сдвигового регистра D2 с выхода формирователя напряжения G1 подано напряжение высокого логического уровня, сдвиговый регистр D2 с приходом каждого импульса этой последовательности осуществляет сдвиг напряжения высокого логического уровня от младшего к старшему разряду.

В момент времени t6 на прямом выходе порогового устройства U1 формируется спад импульса напряжения Uвых.1ПУ. В этот момент на инверсном выходе порогового устройства U1 появляется импульсный перепад напряжения Uвых.2ПУ с низкого на высокий логический уровень. Под воздействием этого перепада напряжения на выходе старшего разряда сдвигового регистра D2 появляется напряжение Uвых.РС высокого логического уровня, которое поступает на вход формирователя коротких импульсов U4 и на вход R установки в нулевое состояние счётчика-распределителя канальных импульсов D4, блокируя его переключение независимо от наличия импульсов на его тактовом входе C.

В момент времени t6 на выходе формирователя коротких импульсов U4 появляется кратковременный перепад напряжения Uвых.ФКИ2 с низкого на высокий логический уровень. Этот перепад напряжения поступает на вход R установки в нулевое состояние RS-триггера D1, в результате чего на выходе этого триггера формируется перепад напряжения Uвых.Т с высокого на низкий логический уровень.

Напряжение Uвых.Т низкого логического уровня, поданное на соответствующий вход логического элемента 2И D3 с выхода RS-триггера D1, блокирует прохождение на выход этого логического элемента импульсов напряжения Uвых.1ПУ, при этом на выходе логического элемента 2И D3, а также на тактовом входе C счётчика-распределителя D4 канальных импульсов формируется напряжение низкого логического уровня.

В момент времени t6 на входе формирователя импульсов фиксированной длительности U2 появляется напряжение Uвых.РС высокого логического уровня. Под воздействием этого напряжения формирователь импульсов U2 формирует на своём выходе импульсный перепад напряжения Uвых.ФИ с высокого на низкий логический уровень длительностью τФИ = t7 - t6, где t7 - момент времени окончания наиболее короткой синхропаузы канальной посылки, которая формируется при максимальном значении длительности всех её канальных импульсов.

Выходное напряжение Uвых.ФИ формирователя импульсов фиксированной длительности U2 поступает на вход блокировки порогового устройства U1. При наличии на этом входе напряжения низкого логического уровня на прямом выходе порогового устройства U1 формируется напряжение Uвых.1ПУ низкого логического уровня, а на инверсном выходе - напряжение Uвых.2ПУ высокого логического уровня независимо от изменения напряжения Uвх. на сигнальном входе порогового устройства U1, что, в свою очередь, блокирует переключение RS-триггера D1, сдвигового регистра D2 и счётчика-распределителя канальных импульсов D4.

После окончания синхропаузы на вход дешифратора команд поступает следующая последовательность синхроимпульсов канальной посылки Uвх., при этом вышеописанные процессы периодически повторяются.

Таким образом, в предлагаемом дешифраторе команд счётчик-распределитель канальных импульсов D4 блокирован от переключения на протяжении всей синхропаузы канальной посылки дешифрируемого сигнала, а пороговое устройство U1 - на временном интервале, равном длительности наиболее короткой синхропаузы этого сигнала, что в совокупности повышает защищённость дешифратора команд от импульсных помех во время формирования передатчиком синхропаузы, когда на вход дешифратора команд синхроимпульсы не поступают.

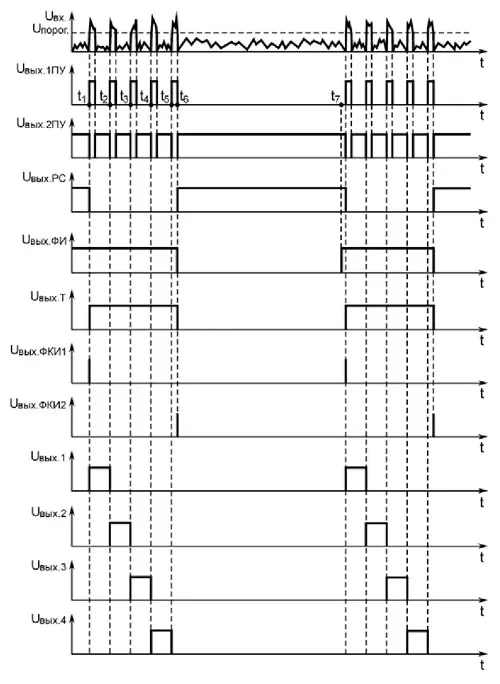

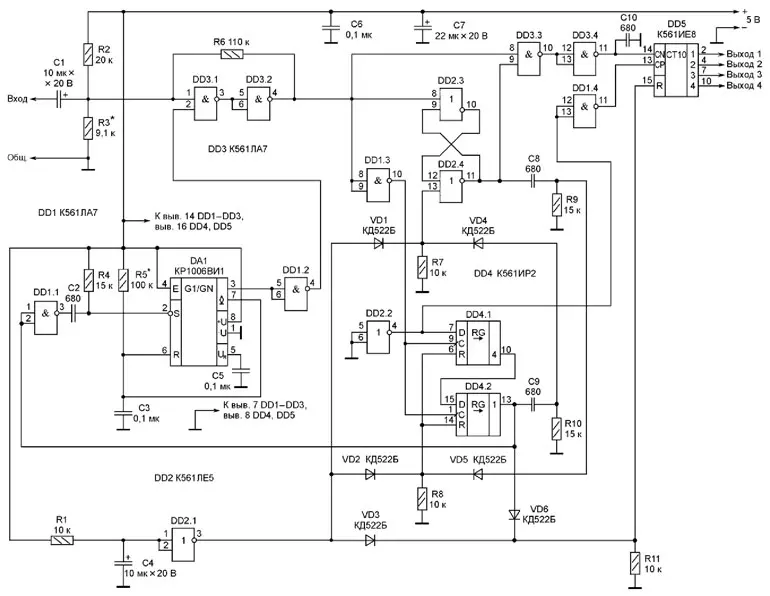

Рис. 3. Принципиальная схема дешифратора команд

На рис. 3 представлена принципиальная схема дешифратора команд. Логические элементы DD1.3, DD3.1, DD3.2, резисторы R2, R3, R6 и разделительный конденсатор C1 образуют пороговое устройство (U1 на рис. 1) - триггер Шмитта. Его прямой выход - вывод 4 логического элемента DD3.2, инверсный выход - вывод 10 логического элемента DD1.3. Вывод 2 элемента DD3.1 - вход блокировки порогового устройства U1. Делитель напряжения R2R3 формирует на выводе 1 элемента DD3.1 напряжение смещения, которое суммируется с поступающим на вход дешифратора команд импульсным напряжением канальной посылки. При достижении этим суммарным напряжением порогов включения и выключения триггера Шмитта на его выходе формируются прямоугольные импульсы напряжения с крутыми фронтом и спадом соответственно. Резистор R6 - элемент положительной обратной связи триггера Шмитта, определяющий разность его порогов включения и выключения.

На интегральном таймере DA1, включённых инверторами логических элементах DD1.1, DD1.2, резисторах R4, R5 и конденсаторах C2, C3, C5 собран формирователь прямоугольных импульсов напряжения фиксированной длительности (U2 на рис. 1). Дифференцирующая цепь R4C2 формирует на своём выходе кратковременный перепад напряжения с высокого на низкий уровень. Этот перепад напряжения запускает включённый по типовой схеме одновибратора интегральный таймер DA1. Длительность выходных импульсов одновибратора задана интегрирующей цепью R5C3 и равна приблизительно 11 мс. Конденсатор C5 - фильтрующий.

Дифференцирующие цепи C8R9VD5, C9R10VD4 - формирователи коротких импульсов напряжения (U3, U4 на рис. 1). На логических элементах DD2.3, DD2.4 собран RS-триггер (D1 на рис. 1). Микросхема DD4 образует пятиразрядный сдвиговый регистр (D2 на рис. 1). Включённый инвертором логический элемент DD2.2 - формирователь напряжения высокого логического уровня (G1 на рис. 1). Логические элементы DD3.3, DD3.4 - элемент 2И (D3 на рис. 1), DD5 - счётчик-распределитель канальных импульсов (D4 на рис. 1). Включённый инвертором логический элемент DD1.4 формирует напряжение низкого логического уровня на входе CP этого счётчика (выв. 13 DD5), что необходимо для переключения счётчика фронтом импульсов, поступающих на вход CN (выв. 14 DD5). Конденсатор C10 - фильтрующий.

Интегрирующая цепь R1C4, включённый инвертором логический элемент DD2.1, диоды VD1-VD3 и резисторы R7, R8, R11 образуют функциональный узел (на рис. 1 условно не показан), обеспечивающий начальную установку RS-триггера, образованного логическими элементами DD2.3, DD2.4, сдвигового регистра DD4 и счётчика-распределителя канальных импульсов DD5 в нулевое состояние при подключении к дешифратору команд напряжения питания. Диод VD6 обеспечивает прохождение в соответствующий момент с выхода пятого разряда сдвигового регистра DD4 (выв. 13 DD4.2) напряжения высокого логического уровня на вход R установки в нулевое состояние счётчика распределителя канальных импульсов DD5 (выв.15 DD5).

Дешифратор команд питается стабилизированным напряжением +5 В. Конденсаторы C6, C7 - фильтрующие.

Монтаж дешифратора команд выполнен навесным способом на макетной плате. В дешифраторе команд применены танталовые оксидно-полупроводниковые конденсаторы К53-16 и керамические конденсаторы К10-17-1а. Конденсатор C3 - плёночный К73-17. Вместо конденсаторов этих типов можно использовать другие аналогичные. Постоянные резисторы - С2-33, возможная замена - С2-23, МЛТ, ОМЛТ.

Диоды КД522Б можно заменить диодами этой же серии или другими подобными, например, серий КД503, КД521. Микросхемы серии К561 заменимы функциональными аналогами серии 564 или импортными.

Налаживание дешифратора команд сводится к установке резистором R3 на выводе 1 логического элемента DD3.1 такого напряжения смещения (приблизительно 1,5 В), при котором обеспечивается восстановление триггером Шмитта формы искажённых шумами синхроимпульсов канальной посылки с амплитудой не менее 1 В. Длительность временного интервала, на котором триггер Шмитта заблокирован во время синхропаузы канальной посылки, корректируют подбором резистора R5.

Литература

1.Войцеховский Я. Дистанционное управление моделями. Пособие моделиста и радиолюбителя. Пер. с польск. Под ред. A.П. Павлова и Н. Н. Путятина. - М.: Связь, 1977, с. 180-186, 188-195.

2.Миль Г. Электронное дистанционное управление моделями / Пер. c нем. B.Н. Пальянова. - М.: ДОСААФ, 1980, с. 45-114.

3.Днищенко В. А. 500 схем для радиолюбителей. Дистанционное управление моделями. - С.Пб.: Наука и техника, 2007, с. 20-37, 352-355.

4.Ильин О. Шифратор команд для многоканальной системы дистанционного пропорционального управления моделями. - Радио, 2021 ,№12, с. 28-31.

5.Ильин О. П. Дешифратор команд телеуправления. Патент РФ № 2754348. - Бюл., 2021, № 25.

Автор: О. Ильин, г. Казань