Справка о применяемости шасси

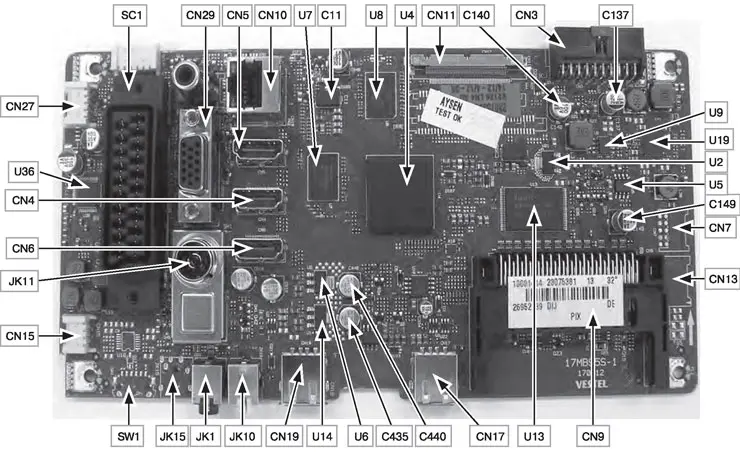

Внешний вид главной платы ТВ шасси 17MB95S-1 изображен на рис. 1. Список моделей ЖК телевизоров, которые выпускаются на рассматриваемом шасси VES2.2E LA (17MB95S-1), приведен в таблице.

Таблица. Модели ЖК телевизоров, которые выпускаются на шасси VES2.2E LA (17MB95S-1)

Производитель (бренд) | Модели ЖК ТВ |

TPV (Philips) | 32PFL3008H/12 32PFL3008K/12 32PFL3008T/12 32PFL3018H/12 32PFL3018K/12 32PFL3018T/12 32PFL3028H/12 |

Sharp | LC-22LE250E-/ V/ К/ RU LC-24LE250E-BK/E-WH LC-24LE250K-BK/K-WH LC-24LE250V-BK/V-WH LC-24LE250RU-BK/RU-WH |

Vestel | 42LD5003F |

Рис. 1. Внешний вид главной платы ТВ шасси 17MB95S-1

Блок-схема шасси VES2.2E LA

Блок-схема шасси VES2.2E LA приведена на рис. 2, а схема соединений для 24-дюймовых моделей ТВ SHARP - на рис. 3. Из схемы видно, что основой шасси является БИС MSD8WB9BX фирмы Mstar. Эта микросхема представляет собой "систему на кристалле" SoC (System-on-a-Chip) и является недорогим решением для цифрового телевидения (IDTV). Приведем ключевые особенности ИМС MSD8WB9BX:

-Front-End-демодулятор стандартов DVB-T/C.

-Мультистандартный аудио- и видеодекодер.

-Видеопроцессор MACEPRO.

-Звуковой процессор для домашнего кинотеатра.

-Поддержка подключения Интернета.

-Двухпоточный декодер для BD-контента.

-Многозадачный процессор (CPU) для ОС и мультимедиа.

-Функции управления периферией и питанием.

Рис. 2. Блок-схема шасси VES2.2E LA (по клику крупно)

Рис. 3. Схема соединений для 24-дюймовых моделей ТВ SHARP (по клику крупно)

Поддерживаемые ИМС

MSD8WB9BX периферийные устройства (см. рис. 2):

-ВЧ вход (42...1005 МГц).

-НЧ вход (ПЦТС (CVBS), R/L_ Audio).

-Разъем SCART.

-Компонентный вход (YPbPr), входы S-Video, для ПК (общий).

-Три цифровых входа HDMI.

-CI-интерфейс.

-Цифровой (SPDIF) и аналоговый аудиовыходы (второй - для наушников).

-Два USB-порта и один Ethernet-RJ45.

-Интерфейс сенсорной панели Touchpad.

Рис. 4. Блок-схема ИМС Si2156

ТВ сигнал с антенны поступает на вход гибридного тюнера, выполненного на основе ИМС Si2156 фирмы Silicon Labs (см. блок-схему на рис. 4). Тюнер принимает и обрабатывает как аналоговые, так и цифровые ТВ сигналы всех мировых эфирных и кабельных стандартов. Основные функциональные возможности ИМС Si2156:

-Стандарты аналогового ТВ: NTSC, PAL/SECAM.

-Стандарты цифрового ТВ: ATSC/ QAM, DVB-T/C, ISDB-T/C, DTMB.

-Частотный диапазон: 42...1002 МГц.

-Соответствие спецификациям A/74, NorDig, D-Book, C-Book, ARIB, EN55020, OpenCable™.

-Интегрированные полосовые (SAW) фильтры и усилитель LNA.

-Не требуется настройки и калибровки прибора.

-Цифровая архитектура с низкой ПЧ.

-Интегрированные канальные фильтры.

-Гибкий выходной интерфейс, включающий выходы ALIF на аналоговый ТВ демодулятор и DLIF на цифровой.

-Напряжения питания 3,3 и 1,8 В.

-Технология CMOS.

-Управление по интерфейсу I2C.

-32-выводный корпус QFN (5x5 мм).

Цифровые и аналоговые выходы ИМС тюнера в схеме объединены (это логично, т.к. одновременно цифровой и аналоговый сигналы не обрабатываются). По общим линиям (на рис. 2 - цепь DIGITAL IF_T/C) сигналы поступают непосредственно на вход Front End SoC для демодуляции и дальнейшей обработки.

На вход SoC могут поступать цифровые аудио- и видеосигналы с одного из трех входов HDMI1- HDMI3. Сигналы на этих входах представляют собой три пары дифференциальных сигналов данных HDMI1(2,3)_RX0±-RX03± и одну пару тактовых сигналов HDMI1(2,3)_RX CLK±. Вначале сигналы поступают на коммутатор в составе процессора, а с его выхода выбранный пользователем сигнал подается на декодер HDMI, который преобразует дифференциальные сигналы в 8-разрядные коды, затем этот цифровой сигнал обрабатывается SoC так же, как и оцифрованные аудио- и видеосигналы с аналоговых входов (на рис. 2 - ANALOG AUDIO/VIDEO INTERFACE).

Наличие у SoC CI-интерфейса позволяет установить CAM-модуль (Condition Access Module) условного доступа, что дает возможность приема платных программ эфирных и кабельных операторов, использующих различные системы кодирования.

Наличие USB-интерфейса (2 порта) позволяет подключать к ТВ различные устройства для расширения его функционала, например, Flash-памяти с аудио- или(и) видеоконтентом, модулей беспроводной связи и т.д.

ИК порт в составе SoC (на рис. 2 - IRIN) служит для подключения ИК приемника, принимающего команды от пульта ДУ.

Универсальные порты ввода-вывода SoC (на рис. 2 - GPIO) запрограммированы для реализации различных функций, в частности: контроль подключения внешних устройств, контроль аварийного состояния шасси, поддержка клавиатуры, управление LED-подсветкой, питанием ЖК панели и т.д.

Для подключения ТВ к локальной сети можно использовать Ethernet-порт в составе SoC.

Для хранения промежуточных данных SoC использует динамическую память DDR3-SDRAM (архитектура 64/128 Мх16 бит), которая подключена через интерфейс RAM. Управляющая программа шасси (ПО) хранится во Flash-памяти с произвольным доступом (архитектура 128/256 Мх8 бит), она подключена к SoC через интерфейс NAND FLASH. К интерфейсу SPI FLASH подключена память с последовательным интерфейсом SPI (16 Мбит), в которой хранятся пользовательские данные и настройки.

В левом верхнем углу на рис. 2 показана структура силовой части (Power Block) главной платы шасси, а именно - интегральных стабилизаторов, формирующих из напряжений блока питания питающие напряжения для ИМС шасси. Все выходные напряжения блока питания (24,12 и 5 В) и стабилизаторов, размещенных на главной плате, контролируются узлом защиты от короткого замыкания Short CCT Protection. В аварийной ситуации он формирует сигнал Protect, который через универсальный порт поступает в SoC для анализа и управления(отключения) блоком питания.

В результате обработки видеосигнала на выходах ИМС формируются цифровые сигналы основных цветов R, G, B и синхросигналы, которые подаются на контроллер интерфейса LVDS (на рис. 2 - LVDS Interface). Он формирует из этих сигналов RGB пять пар дифференциальных сигналов в стандартном или одиночном (single) режиме (4 пары - данные, 1 пара - синхросигналы), или 10 пар в удвоенном (duble) режиме (8 пар данных, 2 пары - синхросигналы). Стандартный режим LVDS используется для подключения ЖК панелей с разрешением WXGA или HD Ready (1366x768 пикселов), а удвоенный режим LVDS - для ЖК панелей c разрешением HD (1720x1080 пикселов).

Для контроля внешних узлов и ИМС в SoC имеется цифровой интерфейс I2C (связь с ИМС тюнера, с цифровым звуковым процессором), а для передачи цифрового звука на звуковой процессор - интерфейс I2S.

Обработка звуковых сигналов на рассматриваемом шасси выполняется мультистандартным звуковым ТВ процессором в составе SoC. Приведем его основные возможности:

-аудиодекодер звуковой ПЧ (SIF);

-демодулятор систем BTSC, A2, EIA-J;

-демодулятор NICAM/FM/AM;

-собственно цифровой звуковой процессор DAP (НЧ канал, регулировки баланса, громкости, тембра, MUTE, виртуальное стерео и т.д.);

-расширенный звуковой процессор (Dolby, SRS, BBE, QSound, Audissey);

-декодер цифровых форматов MPEG1, MPEG2 (Layer I, II), MP3, Dolby Digital, AAC-LC, HE-AAC, WMA.

Если пользователем выбран аналоговый вход, то звуковой сигнал с него оцифровывается, поступает на вход селектора, а с него - на цифровой аудиопроцессор. После обработки (компрессия, регулировка тембра, эквалайзер, функции SRC, BBE, BASS и т.д.) сигнал в формате I2S (последовательные данные двух каналов с частотой дискретизации от 8 до 192 кГц и тактовые сигналы) подается на вход цифрового усилителя мощности типа TAS5717/ TAS5719. Сигналы с цифровых входов ТВ не нуждаются в оцифровке. Поэтому они через селектор поступают на DAP.

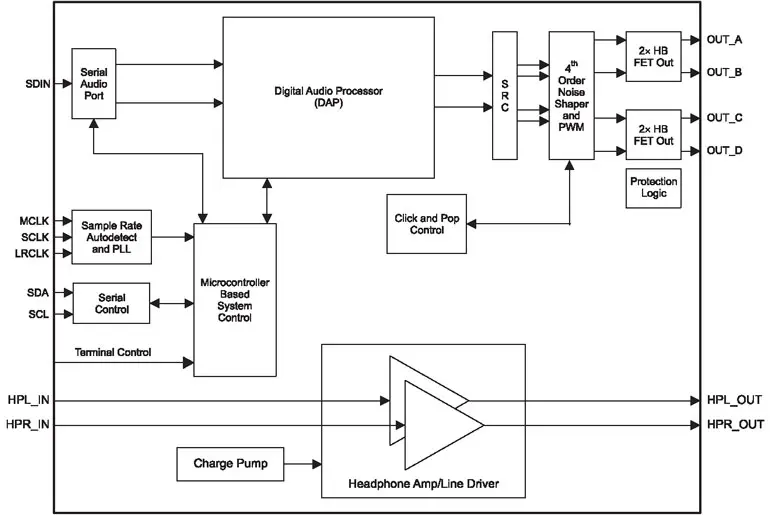

Рис. 5. Блок-схема ИМС TAS5717/ TAS5719

Звуковой усилитель TAS5717/ TAS5719 класса D с выходной мощностью 2x10/15 Вт включает в себя (см. рис. 5) цифровой звуковой интерфейс I2S, управляющий интерфейс I2C, тактовый генератор с ФАПЧ, звуковой процессор (DAP), схему компрессии динамического диапазона (SRC), ШИМ, схему защиты и два полумостовых выходных каскада на MOSFET-транзисторах, что позволяет использовать его в мостовых схемах с однополярным питанием (4...26 В). Один последовательный цифровой вход ИМС позволяет обрабатывать до двух звуковых каналов в широком диапазоне скоростей передачи данных и совместим с выходами большинства MPEG-декодеров. ШИМ в составе усилителя работает с частотой переключения 352 кГц или 384 кГц в зависимости от скорости входного потока данных. Микросхема имеет встроенные средства защиты выходного каскада от перегрузки и перегрева, а также от низкого напряжения питания. Для управления ИМС (адресный выбор) используется интерфейс I2C, через который она подключена к управляющему микроконтроллеру (МК) в составе SoC.

В составе усилителя TAS5717/ TAS5719 имеется еще и усилитель наушников, на рассматриваемом шасси этот усилитель используется для подачи звуковых сигналов на разъем SCART, а на наушники работает усилитель в составе SoC (HP OUT на рис. 2).

Необходимо отметить еще одну особенность рассматриваемого шасси. Несмотря на его бюджетность, однокристальный процессор MSD8WB9BX опционально поддерживает AVS-декодирование - поддержка разрешения 1920x1080 @ 30 кадров/с, битрейт 20 Мбит/с (размер канала) и двухпотоковое декодирование для 3D-контента. Поэтому такое шасси можно вполне использовать для производства 3D-телевизоров.

Продолжение следует

Автор: Николай Елагин (г. Зеленоград)

Источник: Ремонт и сервис