Основные характеристики и возможности

Основные характеристики и возможности ЖК телевизора LG 22LT360C приведены в таблице.

Таблица. Основные характеристики и возможности ЖК телевизора LG 22LT360C

Характеристика, единица измерения и возможности | Значение и описание |

Тип ЖК панели | TFT LCD HD с диагональю 22" (56 см) |

Формат экрана | 16:9 |

Разрешение | 1366x768 пикселов (HD Ready) |

Задняя подсветка | Светодиодная (Edge LED) |

Наличие одного универсального тюнера (аналогового и цифрового) | Да |

Системы цветности аналогового вещания | PAL, SECAM, NTSC |

Стандарты цифрового вещания | DVB-T/C (MPEG-2/4) |

Телетекст | С памятью на 1000 страниц |

Выходная мощность каналов стереозвука, Вт | 2x5 Вт (Engine Infinite Sound Clear Voice II) |

Яркость, Кд/м2, не менее | 360 |

Динамическая контрастность | 1000000:1 |

Угол обзора, град, не менее | 178 (по вертикали и горизонтали) |

Время отклика пиксела, мс | 5 |

Частота обновления, Гц | 50 |

Поддерживаемые форматы входного сигнала | 480i, 480p, 576i, 576p, 720p, 1080i, 1080p |

Доступные разрешения при подключении к ПК | 640x480, 800x600, 1024x768, 1360x768 |

Поддерживаемые форматы мультимедиа | MP3, WMA, MPEG-4, Xvid, DivX, MKV, JPEG |

Интерфейсные входы-выходы | Коаксиальный антенный вход, компонентный видео (Y, Cb/Pb, CR/P R) и аудио (L, R) входы, SCART, RGB от ПК, VGA от ПК при использовании телевизора в качестве монитора, HDMIx3, USB, RS-232C (сервисный порт) |

Наличие слота CI/PCMCIA | Да |

Наличие таймера сна и защиты от детей | Да |

Потребляемая от питающей сети мощность, Вт, не более | 45 |

Напряжение и частота питающей сети | 100...240 В, 50/60 Гц |

Габариты без подставки, мм | 517x386x42 |

Масса без подставки, кг | 3,7 |

Структурная и принципиальная схемы

В состав ТВ шасси LD2AA входят следующие блоки и узлы:

1.Основная плата (Main Block), на которой размещены:

-центральный процессор IC101;

-тюнер TU3700 (в некоторых моделях - TU1400);

-микросхемы (ИМС) памяти EEPROM IC103 и IC104;

-ИМС памяти EEPROM FLASH MEMORY с архитектурой NAND IC102 и с последовательным доступом FLASH MEMORY IC1401;

-ИМС памяти DDR SDRAM IC1201 и IC1202;

-усилители мощности звуковых сигналов IC501 и IC1800;

-схема сброса на ИМС IC51 и IC7509;

-интерфейсы внешних устройств и узлы подключения внешних разъемов;

-формирователи и стабилизаторы питающих напряжений.

2.Модуль драйвера питания светодиодов задней подсветки (LED driver circuit for TN module).

3.Платы клавиатуры управления, фотоприемника и индикаторов (CONTROL IR&LED).

4.LCD-панель с конструктивно объединенной с ней платой масштабирования (Scaler).

5.Звуковые динамические головки (по одной в каждом канале).

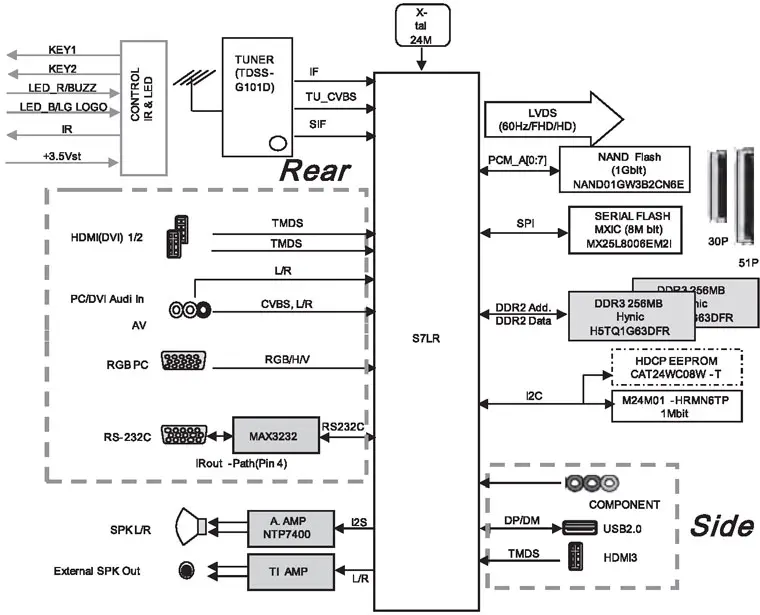

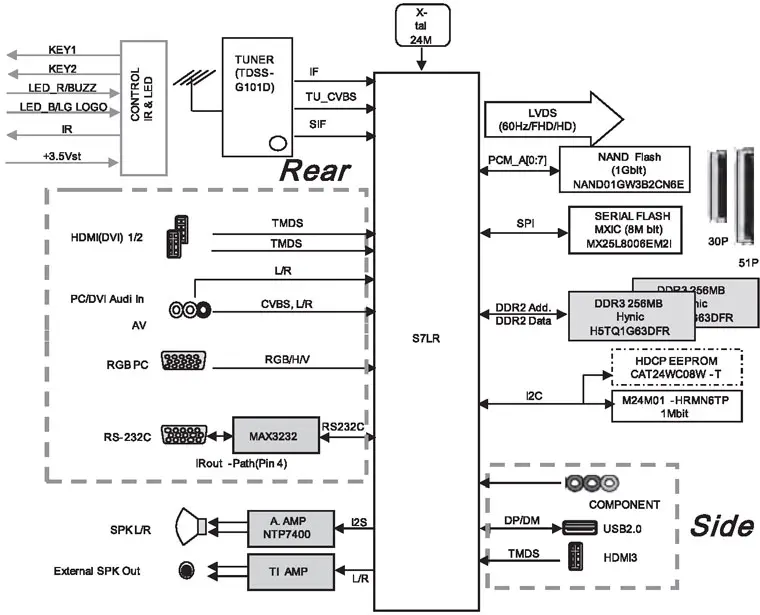

Функциональная структурная схема телевизора приведена на рис. 1.

Рис. 1. Функциональная структурная схема телевизора

Основой схемы является многофункциональный процессор IC101 (LGE2112-T8). На схеме также показаны: тюнер (TUNER), микросхемы памяти, усилители звуковых сигналов и разъемы и интерфейсы подключения внешних устройств: HDMI1/2, PC/DVI, RGB PC, RS-232C (расположены сзади), HDMI3, USB 2.0 и COMPONENT (расположены сбоку), разъемы и интерфейсы подключения ЖК панели (LVDS) и платы клавиатуры управления, фотоприемника и индикаторов (CONTROL IR&LED).

Рассмотрим сигнальные и питающие цепи шасси по принципиальной электрической схеме телевизора, приведенной в архиве ниже.

Тюнер TU3700 типа TDSS-G101D управляется по цифровой шине управления I2C и подсоединен к процессору следующим образом:

-на выв. 2 (RESET) по цепи TUNER_RESET подается сигнал сброса с выв. АВ5;

-на выв. 3 (SCL) и 4 (SDA) по цепям TU_SCL и TU_SDA подаются синхронизирующие сигналы и сигналы данных с выв. AE6 и AD6 соответственно;

-с выв. 6 (SIF) по цепи TU_SIF и через транзистор Q3705 подается сигнал ПЧ звука на выв. AD4;

-с выв. 8 (CVBS) по цепи TU_CVBS и через транзистор Q3703 подается полный видеосигнал на выв. АА8;

-на выв. 9 (IF_AGC) по цепи IF_AGC_MAIN подается сигнал АРУ ПЧ с выв. AD2;

-с выв. 10 (DIF[P]) и 11 (DIF[N]) по цепям IF_P_MSTAR и IF_N_MSTAR подаются цифровые сигналы на выв. АС3 и АЕ3 соответственно.

Тюнер питается напряжением +3.3V, подаваемым на выв. 5 и напряжением + 1.8V, подаваемым на выв. 7. Последнее напряжение получается из напряжения +3.3V с помощью линейного стабилизатора с малым падением напряжения (англ. - LDO), выполненного на микросхеме IC3703 типа AZ1117BH-1.8TRE1 фирмы BCD Semiconductor.

В архиве ниже приведены фрагменты принципиальной схемы телевизора, на которых показано подключение микросхем памяти к центральному процессору IC101 типа LGE2112-T8 (S7LR_DIVX_MS10) фирмы MSTAR. Могут также использоваться процессоры типов LGE2111A-TE, LGE2111A-T8, LGE2111A-VD или LGE2111A-W1.

В левой верхней части рисунка показана ИМС энергонезависимой Flash-памяти с NAND-структурой IC102 типа NAND01GW3B2CN6E фирмы NUMONYX с параллельным интерфейсом, объемом памяти 1 Гбит и организацией памяти 128 Мх8. Кроме нее с равным успехом могут применяться микросхемы типа H27U1G8F2BTR-BC фирмы HYNIX, TC58NVG0S3ETA0BBBH фирмы TOSHIBA, HY27UF082G2B-TPCB фирмы HYNIX или K9F1G08U0D-SCBO фирмы SAMSUNG. Выводы ИМС по цепям PCM_A[0-7] подключены к выв. W20, V20,W22, AB18, AA20, AA21, Y19, AB17 процессора IC101, а по цепям F_RB, PF_OE, PF_CE0, PF_CE1, PF_ALE, PF_WE, PF_WP - к выв. AD19, AC19, AD18, AC18, AE17, AD17 и AC17 соответственно.

ИМС последовательной памяти HDCP EEPROM (High-Bandwidth Digital Content Protection - протокол защиты широкополосных цифровых данных) IC103 (показана внизу схемы) типа CAT24WC08W-T фирмы CATALYST Semiconductor или CAT24C08WI-GT3-H-RECV(TV) фирмы ON Semiconductor с объемом памяти 8 К (1 Кх8) подключена к выв. Р23 и Р24 процессора IC101 по цифровой шине I2C.

ИМС последовательной памяти EEPROM IC104 (также показана внизу схемы) типа AT24C256C-SSHL-T фирмы ATMEL или типа M24256-BRMN6TP фирмы STMicroelectronics имеет организацию памяти 32Кх8 и также управляется по цифровой шине I2C с тех же выводов процессора.

В архиве (см. ниже) приведен фрагмент принципиальной схемы телевизора, на котором показано подключение ИМС последовательной Flash-памяти IC1401 типа MX25L8006EM2I-12G фирмы MACRONIX или W25Q80BVSSIG фирмы WINDBOND. ИМС подключена к процессору следующим образом: ее выводы по цепям FLASH_WP, SPI_CS, SPI_SD0, SPI_SD1, SPI_SCK - к выв. L5, C3, B1, B2, A2 процессора.

С процессором IC101 связаны две микросхемы DDR SDRAM (Double Data Rate Synchronous Dynamic Random Access Memory - синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных) IC1201 и IC1202 типа H5TQ1G63DFR-H9C фирмы HYNIX или K4B2G1646C-HCK0, K4B1G1646G-BCH9, K4B2G1646C фирмы SAMSUNG или NT5CB64M16DP-CF фирмы HYNIX объемом памяти 1 Гбит.

В архиве приведен фрагмент принципиальной схемы телевизора, на котором показано подключение звукового процессора IC501 типа NTP-7500L или STA380BW фирмы STMicroelectronics. ИМС, управляемая по цифровой шине I2C, представляет собой двухканальный цифровой звуковой процессор (DSP) с усилителем мощности в одном корпусе.

Система обеспечивает малый уровень шумов и высокую помехозащищенность в аудиотракте, в том числе благодаря наличию DSP, а также системы цифрового преобразования сигнала с низким уровнем шумов и низким коэффициентом искажений, эффективного усилителя класса D и FFX™-модулятора (Full Flexible Amplification). Модулятор увеличивает эффективность работы системы не только на максимальной громкости, но и при прослушивании при низком уровне выходного сигнала, а именно в таком режиме используется аудиосистема большую часть времени, что позволяет сократить до минимума затраты энергии.

ИМС соединяется с процессором IC101 следующим образом:

-выв. 9 (SDATA) по цепи AUD_LRCH, 10 (WSK) по цепи AUD_LRCK, 11 (BCK) по цепи AUD_SCK, 12 (SDA) по цепи AMP_SDA и 13 (SCL) по цепи AMP_SCL подсоединены к выв. B9, C10, B10, D8, C8 процессора соответственно;

-выв. 14 (/FAULT) по цепям AMP_MUTE (и через каскад на транзисторе Q501) и POWER_DET - к выв. М4 и Н5 процессора;

-выв. 44 (/RESET) по цепи AMP_RESET - к выв. С7 процессора;

-выв. 47 (CLK_I) по цепи AUD_MASTER_CLK - к выв. С9 процессора.

Через контакты разъема Р501 к выв. 40, 41 и 35, 36 микросхемы подключена динамическая головка левого канала (SPEAKER_L), а к выв. 25, 26 и 20, 21 - правого (SPEAKER_R).

Слаботочная часть ИМС питается от источника напряжения +3.3V_Normal, а сильноточная - от источника напряжения +24V_AMP.

В архиве приведены фрагменты принципиальной схемы телевизора с тремя портами интерфейса высокой четкости HDMI (High Definition Multimedia Interface): HDMI_1, HDMI_2 и SIDE_HDMI, находящимися на боковой части корпуса.

Интерфейс HDMI - это поддерживаемый всеми производителями бытовой электроники стандарт передачи несжатых цифровых аудио- и видеоданных по одному кабелю. Интерфейс HDMI предназначен для соединения источников этих данных с устройствами отображения и цифровыми ресиверами и усилителями звука. При этом интерфейс совместим со стандартом DVI (Digital Video Interface), который регулирует передачу цифрового видеопотока. При передаче по специальному кабелю HDMI аудио- и видеоданные кодируются методом TMDS (Transition Minimized Differential Signaling). Метод основан на применении алгоритма кодирования, конвертирующего 8-битовые сигналы в минимизированный 10-битовый код, что увеличивает скорость и качество передачи. Вместо передачи по дорогим коаксиальным кабелям метод TMDS позволяет передавать сигналы по витым парам. Например, одиночный канал TMDS способен поддерживать разрешение изображения до 1600x1200 точек (UXGA) при частоте обновления экрана 60 Гц.

Контакты показанных на рисунке разъемов соединяются с выводами процессора IC101 следующим образом.

Разъем JK802 (HDMI_1):

-контакты 10 и 12 по цепям CK+HDMI1 и CK-HDMI1 - с выв. J2 и J3 соответственно;

-контакты 7, 9, 4, 6, 1,3 по цепям D0+HDMI1, D0-HDMI1, D1+HDMI1, D1-HDMI1, D2+HDMI1, D2-HDMI1 - с выв. K3, J1, K2, K1, L2, L3 соответственно;

-контакты 15 и 16 по цепям DDC_SCL_1 и DDC_SDA_1 - с выв. Т4 и Т5 соответственно;

-контакт 19 и каскад на транзисторе Q802 по цепи HPD1 - с выв. V5;

-контакт 18 по цепи 5V_DET_HDMI_1 - с выв. Е6.

Разъем JK801 (HDMI_2):

-контакты 10 и 12 по цепям CK+HDMI2 и CK-HDMI2 - с выв. F2 и F3 соответственно;

-контакты 7, 9, 4, 6, 1, 3 по цепям D0+HDMI2, D0-HDMI2, D1+HDMI2, D1-HDMI2, D2+HDMI2, D2-HDMI2 - с выв. G3, F1, G2, G1, H2, H3 соответственно;

-контакты 15 и 16 по цепям DDC_SCL_2 и DDC_SDA_2 - с выв. U6 и R6 соответственно;

-контакт 19 и каскад на транзисторе Q801 по цепи HPD2 - с выв. P5;

-контакт 18 по цепи 5V_DET_HDMI_2 - с выв. F5.

Разъем JK803 (SIDE_HDMI):

-контакты 10 и 12 по цепям CK+HDMI4 и CK-HDMI4 - с выв. AF9 и AC9 соответственно;

-контакты 7, 9, 4, 6, 1,3 по цепям D0+HDMI4, D0-HDMI4, D1+HDMI4, D1-HDMI4, D2+HDMI4, D2-HDMI4 - с выв. AC10, AD9, AC11, DA10, AE11, AD11 соответственно;

-контакты 15 и 16 по цепям DDC_SCL_4 и DDC_SDA_4 - с выв. AD8 и AE8 соответственно;

-контакт 19 и каскад на транзисторе Q803 по цепи HPD4 - с выв. AC8;

-контакт 18 по цепи 5V_DET_HDMI_4 - с выв. B6.

Контакты 13 всех трех разъемов по цепи HDMI_CEC используются для подачи сигнала дистанционного управления CEC_REMOTE_S7. Двунаправленная последовательная шина CEC (Consumer Electronics Control) является опционным компонентом интерфейса HDMI и использует протокол промышленного стандарта AV Link, предназначенного для удаленного управления электронными устройствами. Шина СЕС была разработана для удобства управления различными приборами бытовой электроники при помощи одного пульта ДУ и может поддерживать одновременно до 10 устройств.

Сигнал HDMI_CEC подается через полевой транзистор Q806.

В состав каждого порта входит ЭСПЗУ HDMI_EEPROM, которое подключается по цифровым шинам DDC_SCL_1, DDC_SDA_1; DDC_SCL_2, DDC_SDA_2 и DDC_SCL_4, DDC_SDA_4.

В архиве приведены фрагменты подключения интерфейсных входов-выходов сигналов AV, компонентных видеосигналов и сигналов к контактам разъема SCART.

Контакты расположенного на задней крышке разъема JK1604 используются для подачи AV-сигналов AV_CVBS_IN (вход полного видеосигнала) на выв. W4 процессораIC101, AV_COMP_PC_L_IN и AV_COMP_PC_R_IN (входы левого и правого каналов звука) - на выв. Y9 и AA9 процессора соответственно и AV_CVBS_DET (выход видеосигнала) - с выв. Е5 процессора.

Контакты расположенного сбоку разъема JK1600 используются для подачи компонентных сигналов SIDE_COMP_DET, SIDE_COMP_Y-, SIDE_COMP_Pr+ и SIDE_COMP_Pb+ на выв. D9, W2, V1, Y2 процессора соответственно.

Контакты SCART-разъема JK1602 подсоединены к процессору IC101 следующим образом:

-контакт 22 (AV_DET) по цепи SCI_DET связан с выв. В7:

-контакты 8, 16, 15, 11,7 (ID, RGBIO, ROUT, GOUT, BOUT) по цепям SCI_ID, SCI_FB, SCI_R+, SCI_G+, SCI_B+ связаны с выв. V2, V3, U3, T1, R2 соответственно;

-контакт 20 (SYNC_IN) по цепи SCI_CVBS_IN (или SCI_SOG_IN) связан с выв. Y4;

-контакт 19 (SYNC_OUT) через каскады на транзисторах Q1601, Q1602 по цепи DTV_MNT_VOUT связан с выв. AA1;

-контакты 6 (AUDIO_L_IN) и 2 (AUDIO_R_IN) по цепям SCI_L_IN и SCI_R_IN связаны с выв. AB9 и AA11 соответственно;

-контакт 19 (SYNC_OUT) через каскады на транзисторах Q1601, Q1602 по цепи DTV_MNT_VOUT связан с выв. AA1.

Выходные сигналы звука AUDIO_L_OUT и AUDIO_R_OUT подаются на контакты 3 и 1 разъема JK1602 по цепям DTV/MNT_L_OUT и DTV/MNT_R_OUT с выв. 1 и 7 микросхемы IC1601 типа AS324MTR-E1 фирмы BCD или SN324 фирмы KODENSHI AUK Semiconductor, представляющей собой сдвоенный операционный усилитель с малым энергопотреблением и выполняющий функции коммутатора звуковых сигналов.

На входы микросхемы (выв. 3, 5, 10, 12) подаются сигналы SCART1_Lout, SCART1_Rout, EXT_AMP_R и EXT_AMP_L соответственно. С выходов микросхемы (выв. 8 и 14) снимаются сигналы EXT_AMP_R_IN и EXT_AMP_L_IN соответственно.

Транзисторы Q1807, Q1808, Q1810 выполняют функции блокировки звука.

В архиве приведен фрагмент подключения интерфейсных входов-выходов сигналов RGB через контакты разъема JK1104.

Контакты разъема JK1104 подсоединены к процессору IC101 следующим образом:

-контакты 1, 2, 3 (RED, GREEN, BLUE) по цепям DSUB_R+, DSUB_G+, DSUB_B+ связаны с выв. N2, N3, M3 соответственно;

-контакты 13, 14 (HSYNC, VSYNC) по цепям DSUB_HSYNC, DSUB_VSYNC связаны с выв. P2, P3 соответственно;

-контакты 12, 15 (DDC_DATA, DDC_CLOCK) по цепям RGB_DDC_SDA, RGB_DDC_SCL связаны с выв. D2, D1 соответственно;

-контакт 5 (DDC_GND) по цепи DSUB_DET связан с выв. D5.

На рис. 2 приведен фрагмент подключения интерфейсных входов-выходов сервисного порта RS232C. Он состоит из разъема JK1101 типа DE-9 и микросхемы IC1101 типа MAX3232CDR фирмы Texas Instruments. ИМС представляет собой двухканальный драйвер/приемник, имеет защиту от статического электричества 15 кВ и обеспечивает электрическое взаимодействие цепей асинхронной связи процессора и разъема последовательного порта. Устройство работает на скорости передачи данных до 250 кбит/с.

Рис. 2. Фрагмент принципиальной схемы. Интерфейс RS232C. DC/DC-конвертор 24/12 В. Ключ токовой защиты источника 12 В (по клику крупно)

Сигналы с контактов 2, 3 разъема подаются на входы микросхемы, а с ее выходов по цепям PM_RXD, PM_TXD - на выв. L6, K6 процессора IC101.

На этом же рисунке вверху слева приведена схема понижающего преобразователя DC/DC CONVERTER + 12V_ONLY PSU (Power Supply Unit) - внешнего вторичного источника питания, предназначенного для питания всех узлов телевизора. Преобразователь выполнен на микросхеме IC50 типа MP4460DQ-LF-Z фирмы Monolithic Power (MPS). Это устройство преобразует подаваемое на выв. 8, 9 микросхемы внешнее питающее напряжение 24V в напряжение питания 12V (на выв. 1).

Схема формирователя напряжения 12V EXT Power Out создает напряжение EXT_12V из напряжения + 12V/+15V и выполнена на микросхеме IC52 типа MP5000DQ фирмы Monolithic Power (MPS) - программируемом ограничителе тока и напряжения с термозащитой. Входное напряжение питания подается на выв. 11 IC52, а выходное снимается с выв. 6-10. На выв. 3 подается управляющий сигнал EXT12V_CTRL (сигнал разрешения) с выв. G4 процессора IC101.

Принципиальная электрическая схема ЖК телевизора LG 22LT360C на шасси LD2AA находится здесь.

Продолжение следует

Автор: Геннадий Романов (г. Москва)

Источник: Ремонт и сервис