LAST month, we looked at some issues which arose from the simulation of a binary counter. A question was posted by perro on the EPE Chat Zone asking if the unwanted behaviour of the circuit was due to a problem with the Circuit Wizard simulation he had used, or was something to do with the circuit itself. Perro’s circuit was an asynchronous ripple counter similar to the one presented in Teach-In 2011 Part 6 (Fig.6.37) (EPE April 2011), but with a change of component which may caused it to behave differently from the original. The circuit we looked at last month was asynchronous and this month we will look at a synchronous version. Wewill also discuss the way both types of circuit function in a bit moredelail. First, though, a quick recap of the discussion from last month.

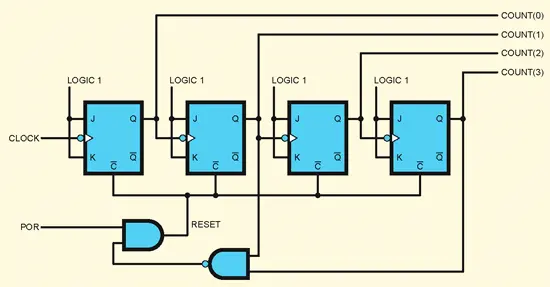

The version of perro’s circuit we discussed, which excludes the seven segment dis play from his simulation, is shown in Fig.1. It uses a NAND gate to detect when the counter’s output value reaches ten (binary 1010) and ‘immediately’ resets the counter to 0000. The reset is not actually immediate because of the response time of the gates and flip-flops, but would not be detectable by a hum an looking at a numerical display. The result is (or should be) that the counter counts from zero (0000) to nine (1001) and so can provide one digit of a decimal number. Perro’s circuit failed to do this, with the counter going to 0100, not 0000 after reaching nine.

Fig.1. Four bit, asynchronous, decade ripple counter

Logic race

Last month, we discussed the simulation of this circuit and the reason for the wrong result, which related to the time delay inherent in all the gates in the circuit, including those

inside the flip-flops. In this circuit we have the possibility of a race condition, which can occur when a signal can take two (or more) paths through a circuit from A to B. In a race, the behaviour of the circuit depends on the order in which the effect of the change at A reaches B via multiple paths.

In this case, the reset, triggered in part by the 1 on the count(1) output (our point A), causes two things to happen inside the count(2) flip-flop, at its internal output latch (our point B). It causes itself to be removed b ecause the counter no longer outputs the value detected by the NAND gate. Also, the count change from 1010 towards 0000 creates an active clock edge (1 to 0 change) on the count(2) flip-flop. If the reset is removed from this flip-flop’s internal latch before the clockedge gets through to the same latch, the clock edge will cause the flip-flop to toggle. Its output will change to 1 rather than remaining at 0 as required.

Last month we demonstrated how changing the relative time delays of gates in the circuit could determine wheOher this problemoccurredornot.

A nasty implication of this type of problem, particularly for commercial designers, is that individual copies of the same circuit may behave differently. Furthermore, because gate delay depends on supply voltage and temperature, the circuit may behave differently under different operating conditions. Advanced logic design tools can help identify sgch timing ambiguities, but it is best to avoid the possitiliSy by design if possible.

Other problems

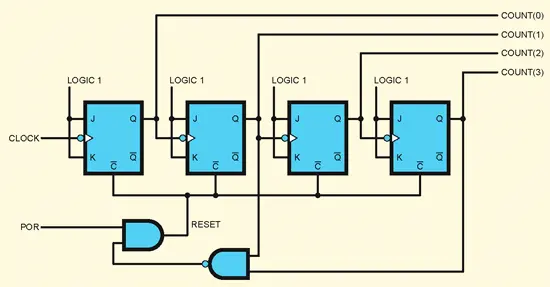

In addition to this timing uncertainty, the circuit in Fig.1 has other potential problems. Wasimonth we also looked at how the output can go through intermediate output values as changes ripple through the circuit from one flip-flop to the next (see Fig.2). Although this happens too fast for a human to detect it could cause false triggering of another circuit.

Fig.2. Details of waveform for counter in Fig.1 as it increments from 0111 to 1000. Note the intermediate values

The point of the reset in the circuit in Fig.1 is to create a base-ten-oriented digital counter from a fundamentally binary or hexadecimal (four-bit binary) circuit. Such circuits are useful when the count value needs to be displayed to people directly because there is no need for additional circuitry to decode a binary value into decimal first. However, reseting a counter at a specific value is not restricted to this application and this general approach is used widely in digital circuit design. In some cases, the number at which the counter resets is programmable, rather than being hardwired to a specific number, as it is in Fig.1. It is, therefore, useful to be able to do this in a reliable way, so in this article we will look at some other circuits for counters, specifically those with synchronous rather than asynchronous operation.

A counter effectively performs the action of adding 1 to the number it currently holds. If we think about this in terms of long addition, then, if the least significant bit (‘1s’ digit) is 0 it will become 1 after the addition of 1. If the least significant digit is 1 then adding 1 will cause a carry of 1 to the next digit (the ‘2s’) and the ‘1s’ digit in the result will be 0 (1 + 1 in binary is 10, which is ‘0 and carry the 1’ in long addition terms). The first bit will therefore always toggle (change 0 to 1 or 1 to 0) when the counter counts. The flip-flops in the circuit in Fig.1 are configured to always toggle when they are clocked (J=K=1), so this requirement is met for count(0).

If the first bit starts at 1 the resulting carry will add 1 to the second digit, so it will toggle, carrying a 1 to the third digit. This process will continue through all the digits until a 0 is reached. The digit which was 0 will toggle to 1, but changes will stop there because there is no carry from this digit to the next. A carry from a digit occurs with a 1 to 0 change on that digit. Thus a negative edge on one digit meansthe next digit must toggle. This is how the circuit of Fig.1 is structured - a negative edge on one flip-flip clocks the next device, causing it to toggle. The ‘rippling’ of a ripple counter corresponds to the propagation of the carry in a long addition in which we add 1 to the counter’s current value. Each carry step takes a finite time, which accounts for the effect seen in Fig.2.

The synchronous route

The circuit is Fig.1 is described as asynchronous because the flip-flops do not all clock together - they are not synchronised. An alternative approach is to clock all of the flip-flops together, which is referred to as a synchronous circuit. If we think about a counter in this way, with reference back to a discussion on long addition, then at the occurrence of each clock the circuit has to determine whether or not a given digit (flip-flop) toggles. Each digit must either toggle or not toggle when clocked. This is different from the circuit in Fig.1, where all the flip-flops are hard-wired to always toggle when clocked. To build a synchronous counter we therefore need a flip-flop with a toggle/don’t toggle control input, often called toggle/hold (T/H) or toggle enable (TE) input.

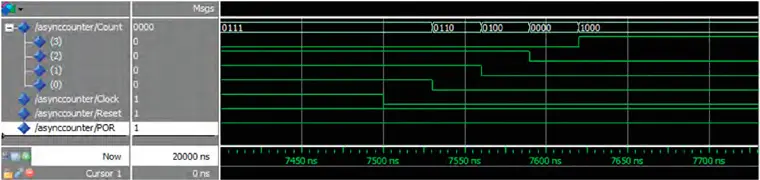

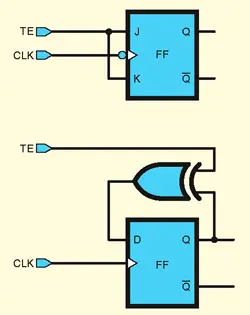

The symbol for a (negative-edge-triggered) toggle/hold flip-flop is shown in Fig.3. This is perhaps not one of the well-known classic flip-flop types (D, JK and RS) but it is an important building block in digital circuits. We can use JK flip-flops with J and K connected together, or a D-type with an XOR gate, to obtain a toggle/ hold function (see Fig.4). Other toggle/ hold flip-flops circuits are possible.

Fig.3. Toggle/hold (toggle enable) flip-flop symbol

Fig.4. Forming a toggle/hold flip-flop from a JK or D-type flip-flop

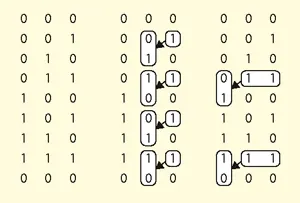

For the synchronous counter to work correctly all the flip-flops’ TE inputs must be simultaneously at the correct value before the clock occurs. Rather than letting the addition carry ripple from bit to bit, in a similar manner to a person laboriously performing a long addition on paper, all the digits are updated together. This is really quite straightforward and follows the same argument as above. The first digit always toggles. The second digit toggles if the first digit is one due to the carry. The third digit toggles if the first two digits are one as the carry propagates through both. Fig.5 shows this pattern visually in a 3-bit binary sequence. In general, a digit toggles whenever all lesser significant digits are 1.

Fig.5. Patterns in binary counting. These relate to the carries which occur when adding 1 to the current count value in binary addition

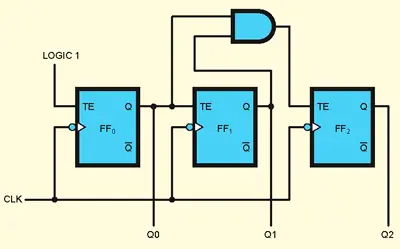

The circuit in Fig.6 is a 3-bit synchronous binary counter based on the arguments above. The first bit always toggles, so the first flip-flop has its toggle/hold wired to logic 1. The second bit (Q1) toggles if the first bit (Q0) is 1, so we connect Q0 to the Toggle Enable control of the second flip-flop. The third bit (Q2) toggles when both Q0 AND Q1 are 1, so we use an AND gate to obtain this function, connecting its output to the TE control of the third flip-flop. This circuit is synchronous because all the flip-flops are clocked together.

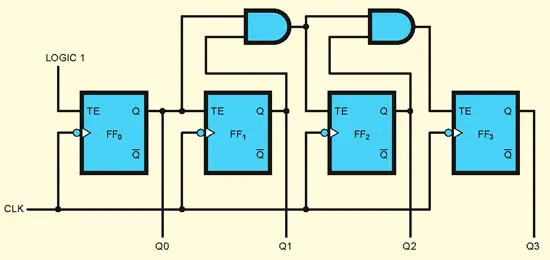

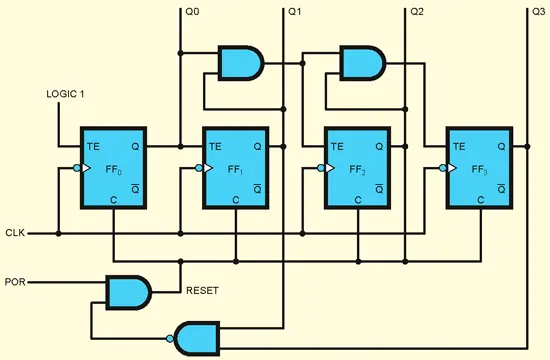

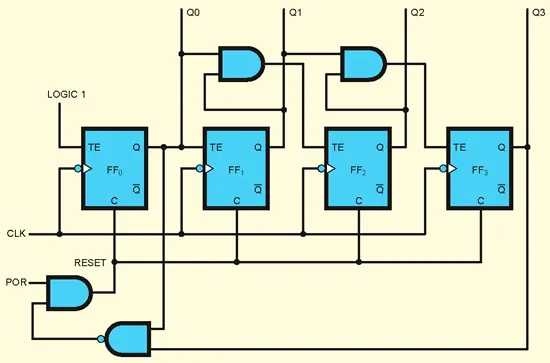

The structure of the synchronous counter follows a pattern, so it easy to extend the circuit in Fig.6 to add more bits. Fig.7 shows a 4-bit version. Adding more bits is simply a matter of including more copies of the TE flip-flop and AND gate stage for all but the last and first bits.

Fig.6. 3-bit synchronous counter using toggle/hold flip-flops

Fig.7. 4-bit synchronous counter using toggle/hold flip-flops

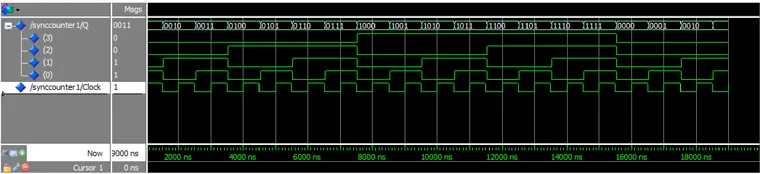

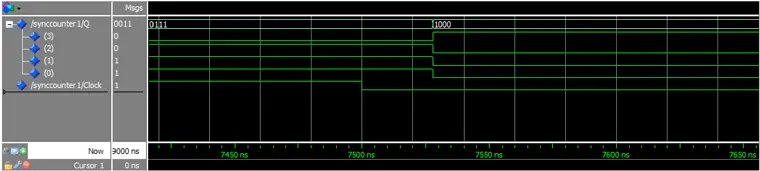

Fig.8 shows a simulation of the circuit in Fig.7. Fig.9 shows a zoom-in to the 0111 to 1000 change, a similar time point to Fig.2. Unlike the circuit in Fig.1, no intermediate output values are produced. The circuit in Fig.7 does not suffer from the output ripple effect inherent in the circuit in Fig.1. A synchronous counter with many bits will update its outputs as quickly as one with just a few bits. However, extending the asynchronous structure in Fig.1 makes the counter take progressively longer to settle its outputs.

Fig.8. Simulation of the circuit in Fig.7

Fig.9. Zoom in on the 0111 to 1000 change from Fig.7. Compare with Fig.2

Limits

There are limits to the synchronous counter however. The outputs of all the AND gates must have settled to the correct value before the next active clock edge. This determines the maximum clock frequency, but as long as this requirement is met the update process is hidden from a user (or other circuitry) looking at the counter’s outputs.

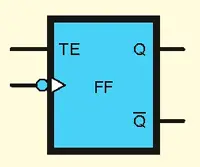

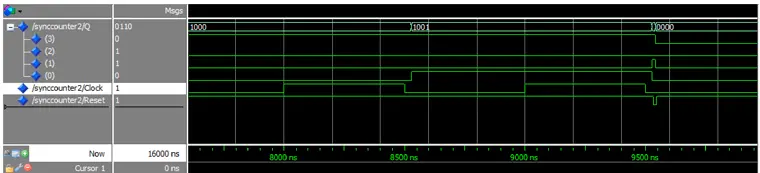

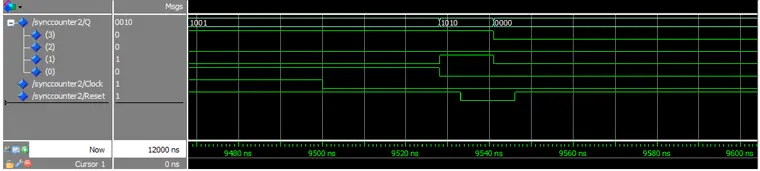

It is straightforward to make a synchronous decade counter using the same approach as Fig.1 - this circuit is shown in Fig.10. It uses toggle/ hold flip-flops with asynchronous clear inputs. The use of asynchronous resets means that the circuit is not really fully synchronous - the reset is not under the control of the clock. Fig.11 and Fig.12 show a simulation of the circuit in Fig.10 zoomed in to the point where the reset occurs. The output does not change cleanly from nine (1001) to zero (0000) because the circuit must output ten (1010) for long enough for the reset to take effect.

Fig.10. A 4 bit synchronous decade counter using toggle/hold flip-flops with asynchronous reset

Fig.11. A 4 bit synchronous decade counter using toggle/hold flip-flops with asynchronous reset

Fig.12. A closer zoom on the reset action from Fig.11

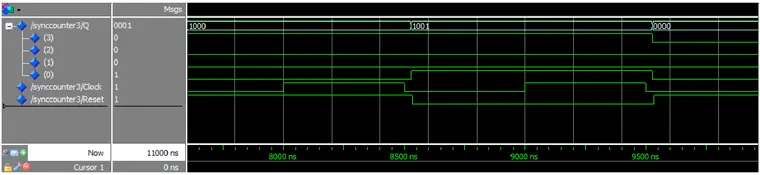

Fig.13. 4-bit synchronous decade counter using toggle/hold flip-flops with synchronous reset

It is possible to design flip-flops with synchronous reset (clear) inputs, rather than the asynchronous resets most common in 4000 and 74 series devices. These flip-flops do not reset immediately when the reset is applied, but also require an active clock edge. To build a decade counter with synchronous reset flip-flops we need to detect nine (1001) to apply the reset rather than ten, this is shown in the circuit in Fig.13. Simulation waveforms of the rest as the count goes from nine to zero are shown in Fig.14.

Fig.14. Simulation of the circuit in Fig.12 zoomed in on the 1001 to 0000 change due to the reset from the NAND gate. Compare with Fig.11 and Fig.12

When the fully synchronous counter reaches nine the NAND gate output goes high producing an active clear input into each of the flip-flops. However, unlike in the previous circuits, they do not reset almost immediately. The counter remains outputting value nine with the reset applied until the next active clock edge. At this point the flip-flops’ internal logic overrides the toggle/hold action and sets their stored value to 0 - the counter resets to zero shortly after the clock edge and does not temporarily output the value ten. In this circuit the reset pulse lasts for a complete clock cycle and does not have the glitchlike characteristic of the circuits in Fig.1 and Fig.10. The counter changes from nine to zero cleanly, without ever outputting ten.

A fully synchronous design has the advantage of predictable and reliable circuit behaviour and is therefore widely used. The power consumption may be higher than an asynchronous version of the same circuit, because all of the flips-flops clock all the time, rather than just when they are need to change state. However, designers of large digital circuits have developed a variety of techniques for making synchronous circuits power efficient.

Author: Ian Bell