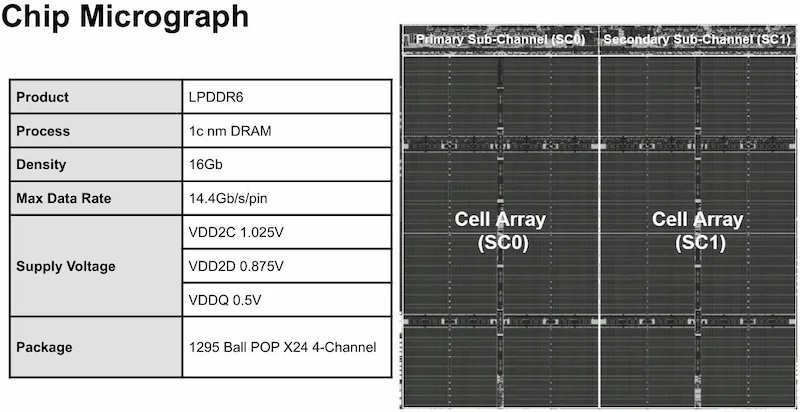

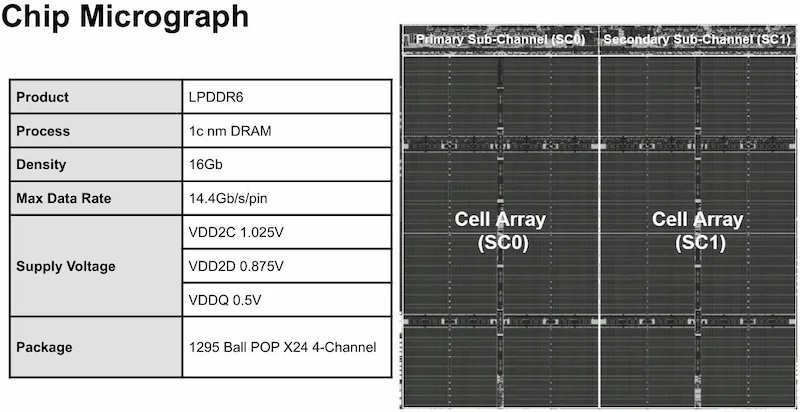

LPDDR6 SDRAM chip micrograph from SK hynix presentation

SK hynix showcased its cutting-edge 16 Gb LPDDR6 SDRAM at the International Solid-State Circuits Conference (ISSCC) 2026. The new memory implements the JEDEC LPDDR6 standard, delivering up to 14.4 Gb/s per pin at 1.025 V while reducing power consumption by 20% and boosting bandwidth by 50% compared to previous generations.

LPDDR6 SDRAM chip micrograph from SK hynix presentation

Compared to LPDDR5/LPDDR5X, LPDDR6 offers higher clock speeds (up to 2,677 MHz), a fixed 2:1 clock-to-write ratio, and enhanced efficiency for demanding applications.

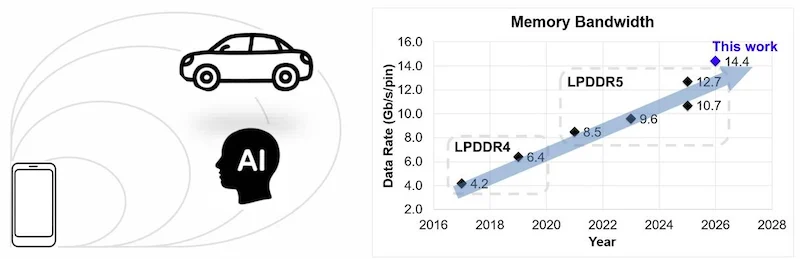

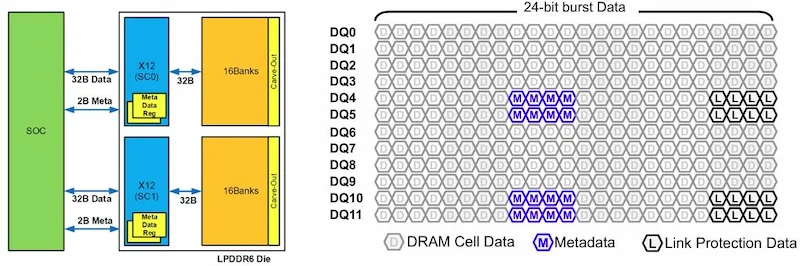

LPDDR6 dual-subchannel topology

SK hynix highlighted five architectural advancements:

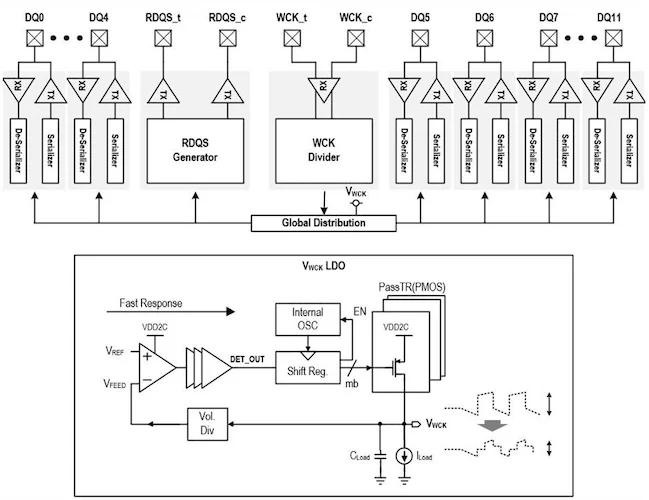

WCK distribution network and global LDO regulator diagram

Dynamic write NT-ODT with test results

The new LPDDR6 targets high-performance mobile devices (smartphones, tablets), edge AI computing, automotive intelligence, and AI data centers, where power efficiency and high bandwidth are critical.

By validating LPDDR6 in silicon, SK hynix confirms the standard's real-world potential, paving the way for mass production and broader adoption in on-device AI products.

Metadata integration within data packets illustration