Блок питания

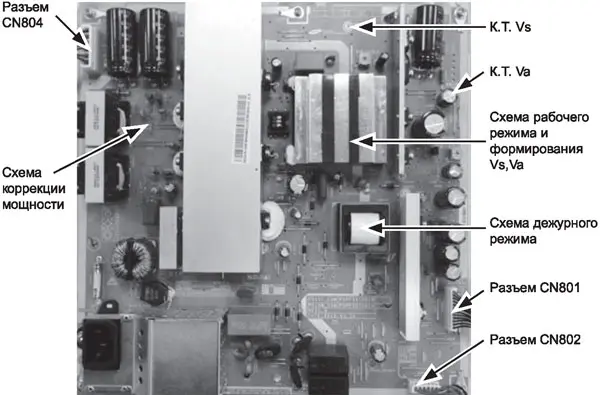

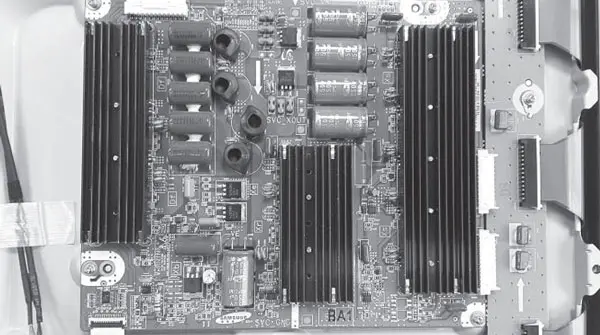

Плата блока питания PSPF381501A (рис. 4) включает в себя источник питания (ИП) дежурного режима, корректор коэффициента мощности (ККМ или PFC), ИП рабочего режима и схему формирования напряжений Vs, Va.

Рис.4. Внешний вид платы блока питания PSPF381501A

Каждый из этих узлов имеет свою систему запуска и управления. К сожалению, автор не располагает оригинальной схемой БП PSPF381501A, но имеется принципиальная схема блока питания BN44-00159 (см. здесь), которая очень близка по схемотехнике, но отличается номиналами вырабатываемых напряжений, наличием/отсутствием регулировок напряжений, способом включения рабочего режима и применяемой элементной базой. В дальнейшем описании БП автор описывает процессы, происходящие на реальной плате (рис. 4). Сетевое питаниедежурного ИП коммутируется через реле RL801. Для запуска дежурного источника сетевое напряжение через терми-сторы NT801, NT802 подается на ШИМ контроллер ICE3BR1765JZ (7-выводная ИМС с отделенным силовым выводом) через обмотку трансформатора TB801 и выпрямитель DX805 CX805. Через 2...3 с, если не срабатывает схема защиты на ИМС ICQ801 (размещена на обратной стороне платы), включается реле RL801 и напряжение сети через двухполупериодный выпрямитель поступает на дежурный ИП. Его выходное напряжение 5,3 В, в отличие от схемы БП на вкладке, подается на регулятор типа LM1117-3.3 (размещен на обратной стороне платы), и его выходное напряжение 3,3 В поступает на основную плату. Контроль напряжения обеспечивается обратной связью на оптроне PC801.

Через контакты реле RL802, которое включается сигналом PS-ON с основной платы, сетевое напряжение поступает на схему ККМ через мостовой выпрямитель DIP. В схему ККМ входят: ШИМ контроллер ML4824, трансформаторы TPA801,802, силовые транзисторы QP801, QP802 и выпрямитель DP801 CP851 CP811.

Рабочий ИП формирует напряжения +5 и +15 В. Источник включается при наличии постоянного напряжения 380 В на выходе ККМ и переключения ШИМ дежурного ИП сигналом PS-ON через оптрон PC802 в рабочий режим (режим повышения выходной мощности), а напряжение на силовом транзисторе ШИМ обеспечивает ККМ - в этом отличие от схемы на вкладке. Напряжение 380 В с выхода ККМ также поступает на схему формирования напряжений рабочего режима Vs, Va. В состав этой схемы входят: ШИМ контроллер ICS801, трансформаторы TS801, TS802, два силовых транзистора QS801, QS802 и вторичные выпрямители напряжений сканирования Vs, адресации Va. ШИМ контроллер включается сигналом VS-ON с платы логики. Работа схемы контролируется ШИМ и симистором QS809 (по шине Va), к выходным выпрямителям подключены регуляторы напряжений Va-adj и Vs-adj. Защиту от короткого замыкания (КЗ) на выходах основных напряжений обеспечивает ИМС ICQ802 типа 74LCX125 с оптронами PC804, PC805. Плата БП подключается к другим платам через разъемы CN801, CN802, CN804. Номиналы напряжений на этих разъемах в рабочем режиме указаны в таблице 3.

Таблица 3. Номиналы напряжений на разъемах ИП

Разъем | Номинальные значения напряжений на выводах разъемов | ||||||

CN804 (питание платы Y) | Vs (контакты 1,2) - напряжение сканирования +207 В | Vg (контакт 4) - напряжение -15 В для питания ключевых транзисторов плат Y и X | Va (контакт 6) -напряжение +58 В для питания платы адресного буфера | Корпус (контакты 3, 5) | |||

CN801 (питание основной платы) | Сигнал PS-ON (контакт 1) включения рабочего режима (активный уровень - +0,145 В) | Напряжение питания дежурного режима (контакт 2) +5 В | Напряжение питания рабочего режима (контакты 7, 8, 12) +5,3 В | Напряжение питания тюнера (контакты 10, 11)+15 В | Напряжение питания УМЗЧ (контакты 4) ±15 В | Корпус (контакты 3, 5, 6, 9) | |

CN802 (питание платы логики) | Корпус (контакт 3) | Напряжение питания платы логики (контакты 1,2) +5,3 В | Сигнал VS-GON (контакт 4) схемы защиты (+0,15 В) | Сигнал PS-ON logic (контакт 5) (+0,145 В) | Сигнал VS-ON (контакт 6) включения схемы формирования напряжений Vs, Va (+3,3 В) | ||

Основная плата

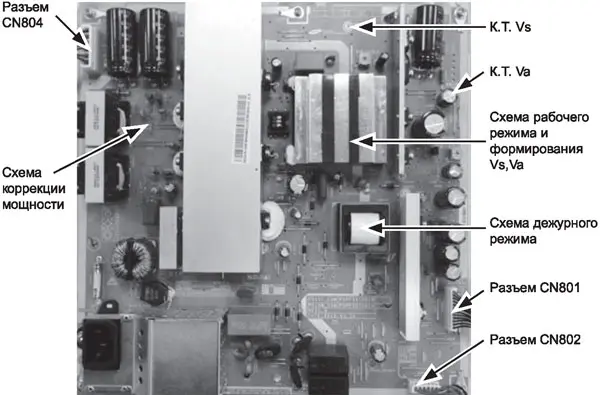

Состав этой платы и назначение элементов почти не отличается от аналогичной платы, используемой в ЖК телевизорах, собранных на платформе X12 (разновидность платформы "Парма", см. [1]). На основную плату рассматриваемого шасси дополнительно установлены разъемы для подключения модуля обновления Evaluation Board и модуля беспроводной связи Bluetooth. Обработка видеосигнала от всех источников проводится в ИМС скалера (центральная ИМС на рис. 5). В остальном набор ИМС соответствует типичной схеме платформы X12, а значит принцип действия и неисправности этой платы аналогичны приведенным в [1]. Сервисный режим также аналогичен по своей структуре приведенному в [1]. Указание на то, что на шасси используется плазменная панель, прописывается в сервисном меню на вкладке Option - LVDS format - PDP. Вход в сервисный режим и принцип работы в нем полностью совпадают с описанным в [1]. На рис. 5 представлен внешний вид основной платы и указаны основные элементы:

-ИМС скалера (на платформе Exo-P, размещена под радиатором, 1 на рис. 5);

-4 микросхемы ОЗУ (2) и микросхема Flash-памяти KLM2G1HE3F (3), в ней хранится основная прошивка;

-переключатель входов HDMI (4);

-видеопроцессор обработки видео- и аудиосигналов от различных входов SDP1101 (5);

-2-канальный усилитель мощности звука TAS5735 (6) и дежурный МК WT61P806 (7);

-трансивер LVDS Parma SDP1005 (8).

Рис. 5. Внешний вид основной платы

Кабельные соединения основной платы с другими устройствами показаны на рис. 1 (см. часть 1).

Плата логики

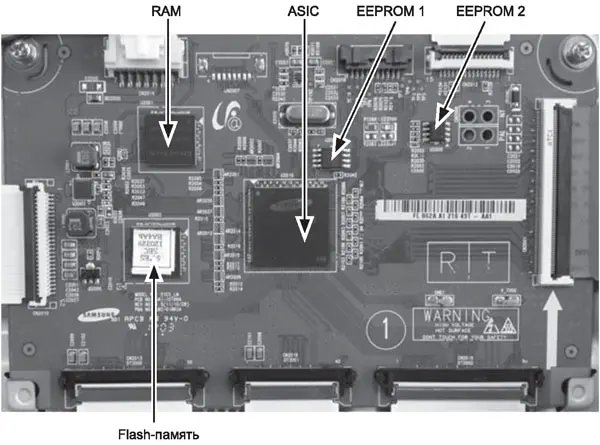

Внешний вид и основные элементы платы логики представлены на рис. 6.

Рис. 6. Внешний вид платы логики

Микросхема программируемой логики ASIC (Application Specific Integrated Circuit) U2010 формирует сигналы управления в соответствии с файлом конфигурации. Эти сигналы поступают на платы X, Y и буфер A, соответственно, через разъемы CN2012, CN2010 и CN2013/2015/2016. Кроме указанной ИМС в состав платы логики входят:

-ОЗУ U2001;

-Flash-память U2002, в ней хранится основная управляющая программа с алгоритмом формирования сигналов сканирования и подсветки для панели PS51E;

-ЭСППЗУ (EEPROM) U2000 объемом 4 кбайт, в ней хранится конфигурация ИМС ASIC. В рабочем режиме она защищена от записи и стирания;

-LED 2000, индикатор работоспособности платы логики;

-разъем CN2008, его контакты 1-2 служат для включения тестового режима;

-разъем CN2009, используется для загрузки файла конфигурации от внешнего программатора;

-процессор гамма-коррекции U2003;

-ЭСППЗУ U2005, быстродействующая Flash-память объемом 16 Мбит с последовательным интерфейсом SPI для хранения значений состояния регистров ИМС ASIC и ее конфигурации в рабочем режиме.

Процессор программируемой логики ASIC формирует сигналы управления ключами Y, X и драйверами буферов адреса и синхронизации по строкам и кадрам. Через гибкие шлейфы на платы X, Y, A подается напряжение питания цифровых элементов этих плат, которое можно контролировать на контактах 1,2 разъемов CN2010-CN2013, CN2016.

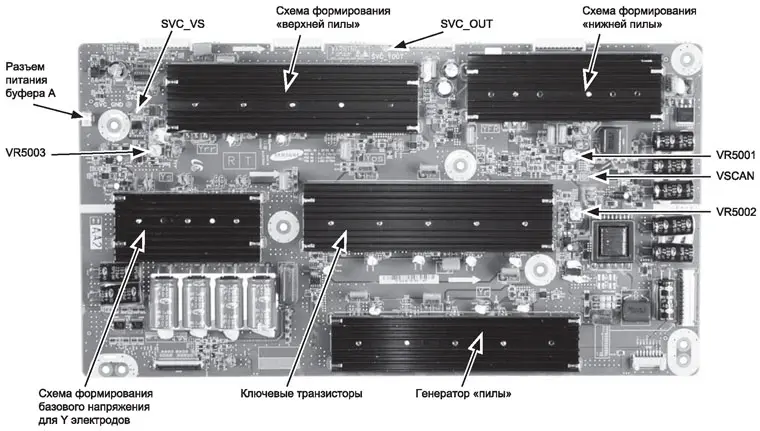

Плата и буфер Y

Плата Y формирует три типа импульсов: сканирующие, стирающие и подсветки. Импульсы формируются с помощью ключей на полевых транзисторах, управляющие сигналы поступают с платы логики (разъем CN2010). Выходные импульсы платы Y через ключи поступают на буфер Y. Общий вид платы Y показан на рис. 7. Все контрольные точки на ней и регулировочные позиции указаны в таблице 4.

Рис.7. Внешний вид платы Y

Таблица 4. Контрольные точки и регулировочные позиции на плате Y

Тип напряжения | Назначение | Регулировка | Действие |

Контрольная точка (КТ)SVC_VS | Напряжение смещения для импульсов подсветки 207 В | В БП VS_ADJ контролируется в КТ SVC-VS относительно КТ SVC-GND (плата Y) и в КТ VS-ADJ (БП) относительно корпуса | При уменьшении напряжения появляется рябь на изображении |

VScan | Напряжение смещения для импульсов сканирования Ve (-186 В) | Регулируется потенциометром VR5002 и контролируется в КТ VSCAN относительно КТ SVC-GND | Уменьшение уровня приводит к нестабильности нижнего уровня пилообразного напряжения (на изображение почти не влияет, но периодически может срабатывать защита и отключать ТВ) |

КТ SVC_OUT | Напряжение смещение для платы Y при адресации(-120 В) | Не регулируется | - |

VR5001(верхний) | - | Регулировка ширины импульса, действующего на электродах Y в начале процесса очистки ячеек после разряда (сброс заряда) | - |

VR5003 (нижний) | - | Регулировка глубины импульса (отрицательного пилообразного напряжения) упорядочивания зарядов | - |

Действие регулировочных резисторов VR5001-VR5003 на форму напряжений на электродах Y показано на рис. 3. Кратко работу платы Y можно описать следующим образом. Из напряжения Vs преобразователями Ys, Ye, основные узлы которых - гибридные ИМС (на рис. 7 скрыты под радиаторами), импульсный трансформатор и электролитические конденсаторы, формируются напряжения Ve, Vsc. Гибридным генератором Yr формируется пилообразное напряжение подсветки, преобразователи Yfr, Yrr совместно с силовыми ключами формируют импульсы переднего и заднего фронтов инициализации. Схема Yps формирует полный сигнал для электродов Y для всех подполей.

Импульсные напряжения через разъемы CN5507, CN5509, CN5010 поступают на плату буфера Y. На плате буфера имеется шесть пар ИМС драйверов типа AN16528A фирмы PANASONIC. Каждая ИМС буфера обслуживает либо четные, либо нечетные строки панели. ИМС AN16528A питается двумя напряжениями:

-+120 В (контролируют на конденсаторах С5507, С5521 С5523);

-+5 В (контролируют на выходе регулятора 78D05).

Непосредственно на выводах ИМС напряжения контролировать нельзя, так как можно повредить герметик, что приведет к ее выходу из строя.

В рабочем режиме на плату поступают напряжения питания, указанные в таблице 5, через разъем CN5008.

Таблица 5. Назначение и регулировка питающих напряжений на разъеме платы Y

Контакты разъема СN5008 | Значение напряжения, В | Назначение и регулировка |

1 | 58 | Напряжение адресации Va, регулируется переменным резистором на плате питания Va-ADJ (КТ Va - TP) в пределах 2% |

2, 3 | 0 | Общий |

4 | 15 | Опорное напряжение на затворах МОП транзисторов ключевых схем. Из него формируется напряжение 5 В для питания элементов схемы |

5, 6 | 0 | Общий |

7 | 207 | Напряжение сканирования Vs, регулируется на плате питания Vs-ADJ (КТ Vs -TP) в пределах 1,5% |

8 | 207 |

Плата и буфер Х

Плата X подключается к Х-электродам через буфер, она формирует сигналы для подполей, которые включают: импульсы подсветки в период горения плазмы, стирающий (сбрасывающий) импульс во время инициализации и напряжение смещения в процессе сканирования и адресации. Сигналы формируются с помощью ключей на полевых транзисторах, входными сигналами служат сигналы с платы логики (LOGIC), поступающие через 15-контактный разъем CN4000. Внешний вид платы Х и формы сигнала (контролируется относительно электродов Y) показаны на рис. 3, 8.

Рис. 8. Внешний вид платы Х

Питание платы Х осуществляется от платы Y через разъем CN4003. Номиналы напряжений и их назначение представлены в таблице 6.

Таблица 6. Назначение и регулировка питающих напряжений на разъеме платы X

Контакты разъема CN4003 | Номинал напряжения | Назначение и регулировка |

13 | 4,9 В | Питание микросхем |

12 | 15,2 В | Питание ключей |

11,4, 5 | Корпус | Общий |

10, 9, 8, 7, 6 | 124,6 В | Напряжение смещение Vb для электродов Х при адресации ячеек |

3 | 111 В | Напряжение смещения Ve (при очистке ячеек), контролируется в КТ Ve и регулируется VR4000 |

1,2 | 207 В | Напряжение Vs подсветки и импульсов сброса |

В состав платы Х входят:

-схема формирования логических уровней Df;

-схема формирования базового напряжения смещения в процессе инициализации Xe;

-схема формирования смещения на электродах в процессе адресации Vb;

-схема формирования импульсов подсветки Xr (пилообразное напряжение);

-схема оконечного формирователя Xs;

-буферные ключи Xg.

Буферная плата Х предназначена в основном для равномерного распределения потенциала по всей площади панели (по Х-электродам), все электроды объединены в одну шину. Суммарное напряжение на Х-электродах можно контролировать осциллографом относительно корпуса панели на любом контакте разъемов шлейфов, подключенных к панели.

На плате Х формируется контрольное напряжение 5 В и напряжение резервного противоаварий-ного канала -124 В. Это рабочие напряжения для платы, в то же время они используются для остановки работы платы Y, если произошла авария на плате X.

Плата адресного буфера

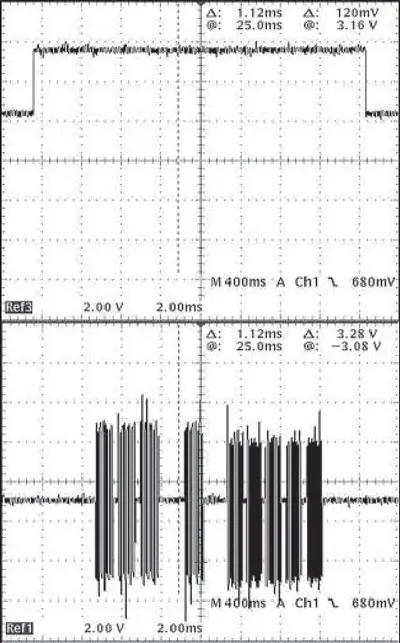

Плата адресного буфера питается напряжением Va, которое поступает от БП через плату Y и подается по внутренним соединениям на подплаты E, G и F. Напряжение Va является также контрольным при аварии в буферах адресной шины, оно используется для выключения платы Y. Сигналы управления от платы логики - импульсы синхронизации (сброс ячеек) и импульсы адресации каждой ячейки - поступают на плату адресного буфера через разъемы CN2013-CN2015, CN2016. Форму этих сигналов можно наблюдать на любом из контактов разъемов (рис. 9).

Рис. 9. Осциллограммы управляющих сигналов на плате адресного буфера

Литература

1.Владимир Петров. Схемотехника, ремонт и регулировка Smart-телевизоров "Samsung UExxD" 6-й серии. Ремонт & Сервис, № 7-9, 2015.

2.Владимир Петров. Регулировка, диагностика и мониторинг узлов, блоков и приборов радиоэлектронной аппаратуры проводной связи, элементов и узлов импульсной и вычислительной техники. Издательство "Академия", 2015.

Автор: Владимир Петров (г. Москва)

Источник: Ремонт и сервис