MIT Twin PUF: два чипа делят уникальный физический отпечаток для прямой аутентификации

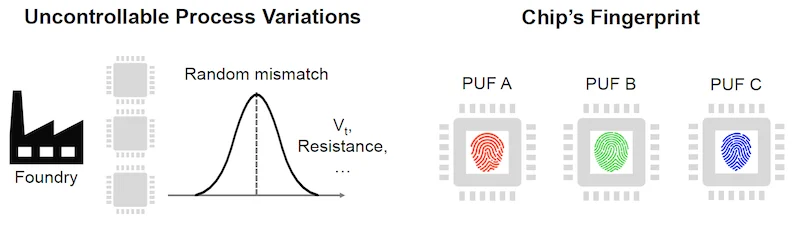

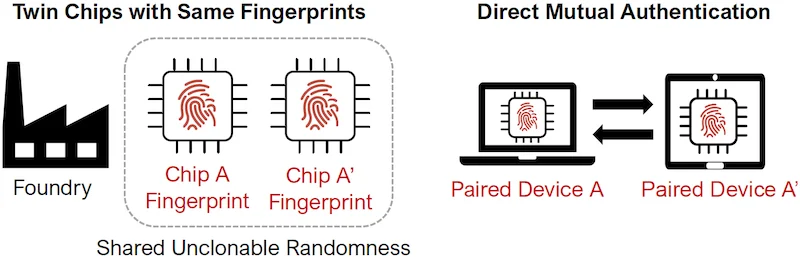

Учёные Массачусетского технологического института (MIT) представили новую технологию изготовления чипов по CMOS-процессу, которая позволяет двум чипам делить уникальный физический "отпечаток пальца". Это даёт возможность прямой взаимной аутентификации без хранения секретных ключей на сторонних серверах. Новая система "twin PUF" существенно повышает безопасность оборудования, конфиденциальность и энергоэффективность для устройств Интернета вещей и edge-систем.

MIT Twin PUF: два чипа делят уникальный физический отпечаток для прямой аутентификации

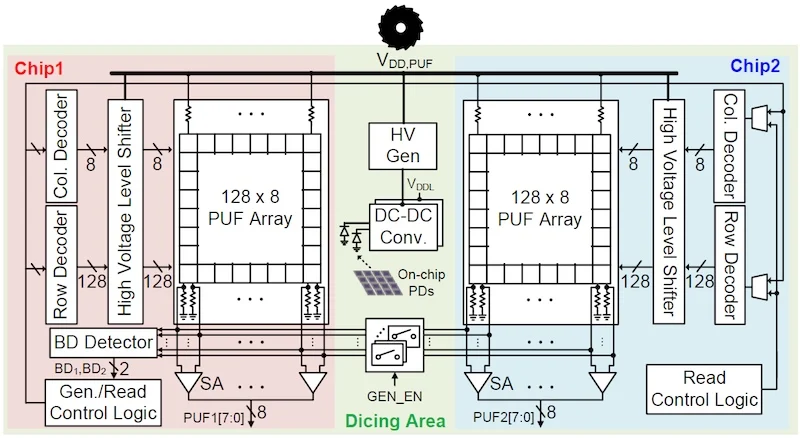

На этапе обработки пластины (до разделения на кристаллы) вдоль краёв двух соседних чипов размещаются специальные транзисторные структуры, соединённые металлическими слоями. Встроенные фотодиоды преобразуют свет от LED в энергию, которая питает схему и вызывает контролируемый пробой затворного оксида в выбранных транзисторах. Из-за естественных вариаций производства время пробоя отличается случайным образом, формируя уникальные электрические состояния - отпечаток PUF.

В "двойной" конфигурации четыре транзистора (по два на каждом чипе) участвуют в одном событии пробоя, создавая взаимодополняющие, но идеально совпадающие ответы. После разделения пластины два чипа образуют пару с коррелированной случайностью.

Процесс изготовления: общий пробой оксида затвора с питанием от LED

Традиционный PUF против MIT Twin PUF: отказ от серверов

Технология особенно перспективна для:

Новый подход переносит безопасность на физический уровень кремния, делая криптографические схемы более надёжными для ресурсосберегающих устройств.

Прототип: массивы PUF 128 × 8, изготовленные по 65-нм CMOS-техпроцессу