Electronics News

Archive : 18 November 2014 год

Researchers at the University of Southampton have found a way to produce more reliable and robust photonic chips.

Researchers at the University of Southampton have found a way to produce more reliable and robust photonic chips.

Until now, testing and characterising optical chips has been difficult as the light travelling in them is confined in the silicon and therefore cannot be seen or measured.

The new method developed by the Southampton team enables the flow of light in photonic chips to be 'seen' for the first time.

Called ultra fast photomodulation spectroscopy (UPMS), it uses ultraviolet laser pulses of femtosecond duration to change the refractive index of the silicon in a tiny area on the chip.

Project leader Dr Roman Bruck explained: "Monitoring the transmission of the chip while the refractive index is locally changed gives a precise picture of how the light flows through it.

"This allows testing of individual optical elements on the chip, a crucial step in the design optimisation to ensure its flawless operation. Because the changes induced by the technique are fully reversible, this testing method is non destructive and after testing, the chip can be used for its intended application."

Dr Bruck says the technique is fast, robust and has the potential to be used for industrial testing in the photonics industry.

Author

Laura Hopperton

Source: www.newelectronics.co.uk

Altera and IBM have developed an FPGA based acceleration platform that connects an FPGA coherently to a POWER8 CPU via IBM's Coherent Accelerator Processor Interface (CAPI). By sharing virtual memory between the FPGA and processor, the reconfigurable hardware accelerator is said to improve system performance, efficiency and flexibility in high performance computing and data centre applications.

Altera and IBM have developed an FPGA based acceleration platform that connects an FPGA coherently to a POWER8 CPU via IBM's Coherent Accelerator Processor Interface (CAPI). By sharing virtual memory between the FPGA and processor, the reconfigurable hardware accelerator is said to improve system performance, efficiency and flexibility in high performance computing and data centre applications.

"Our work with the OpenPOWER Foundation has enabled us to deliver highly flexible heterogeneous compute platforms that target Power based systems," said David Gamba, senior director of Altera's computer and storage business unit. "Altera is at the forefront of supplying Power users reconfigurable hardware accelerators based on CAPI that are supported with an OpenCL programming model. The result is highly optimised accelerators that deliver optimal FLOPs/Watt/dollar."

According to the partners, by using CAPI to attach FPGA accelerators coherently to the fabric of a POWER8 processor and main system memory, the FPGA appears to be another POWER8 processor core.

The move is supported by the Altera SDK for OpenCL, which allows developers to develop custom FPGA based accelerators.

Meanwhile, Nallatech has created an OpenPOWER CAPI Development Kit for POWER8 that features its 385 card, pictured, said to be the first CAPI FPGA accelerator card.

Author

Graham Pitcher

Source: www.newelectronics.co.uk

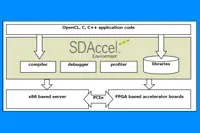

In a move which it says will bring better power performance to data centres, Xilinx has launched SDAccel. The package, part of Xilinx' SDx family, combines an architecturally optimising compiler, supporting OpenCL, C and C++, libraries, development boards, and a 'CPU/GPU like' development environment.

In a move which it says will bring better power performance to data centres, Xilinx has launched SDAccel. The package, part of Xilinx' SDx family, combines an architecturally optimising compiler, supporting OpenCL, C and C++, libraries, development boards, and a 'CPU/GPU like' development environment.

Giles Peckham, European marketing manager for Xilinx, said there are two issues facing data centres. "PCI Express based apps need to run at less than 25W, but are performance limited. Apps that need higher performance are power limited, so developers tend to use GPUs because they are more powerful. However, both approaches have reached a performance per Watt limit." He added that developers of such applications don't have to understand hardware or FPGA place and route. "We're offering a design environment that allows FPGAs to be used as if they weren't there."

According to Xilinx, SDAccel's compiler delivers up to 25 times better performance/Watt compared to CPUs or GPUs. It allows software developers to use new or existing OpenCL, C and C++ code to create high performance accelerators, optimised for memory, dataflow and loop pipelining in a range of data centre applications.

Xilinx says developers can use a familiar workflow to optimise their applications and to take advantage of FPGA platforms without having to know about FPGAs. The integrated design environment executes the application on data centre ready FPGA platforms, with automatic instrumentation insertion for all supported development targets.

SDAccel will be available initially for x86 based processors, but Peckham said that ARM based devices will be addressed in 2015.

Author

Graham Pitcher

Source: www.newelectronics.co.uk

Belgian nanoelectronics research centre imec has partnered with US fabless company MegaChips to develop ultra low power (ULP) short radio technology for smart homes and buildings.

Belgian nanoelectronics research centre imec has partnered with US fabless company MegaChips to develop ultra low power (ULP) short radio technology for smart homes and buildings.

Specifically, the two organisations are working to create a multi standard, sub GHz radio solution compatible with ZigBee 900MHz and IEEE802.15.4g, built on CMOS technology.

The aim is to achieve a transmit power two times lower than current state of the art (60mW) and a receive power five to 10 times lower (6mW).

"We are pleased that MegaChips has joined our R&D programme to strengthen our research ecosystem," said Harmke de Groot, program director of ULP circuits and devices at imec/Holst Centre. "Combining our partners' know how with our expertise in radio design and technology enables new innovative products for the IoT while significantly shortening the time to market for our industrial partners."

Author

Laura Hopperton

Source: www.newelectronics.co.uk