Electronics News

Archive : 11 March 2015 год

A 2D material made from mercury and tellurium is likely to not only feature the properties of graphene, but also to add qualities that graphene misses.

A 2D material made from mercury and tellurium is likely to not only feature the properties of graphene, but also to add qualities that graphene misses.

Professor Cristiane Morais Smith from Utrecht University said: "If we succeed in synthesising it and the material exhibits the combination of exotic properties at room temperature that we predict, a field of fundamental research and technological innovations opens up that lies beyond our imagination." But, as Prof Morais Smith notes, mercury telluride has yet to be created.

Theoretical studies suggest that mercury telluride would be a semiconductor at room temperature and could be used as a field effect transistor. It is also said to fulfil the conditions required to realise quantum spintronics, because it may host the quantum spin Hall effect at room temperature.

The challenge for theoretical physicists was to find a way to shape a material that could have the potential to realise the quantum spin Hall effect at room temperature in a honeycomb structure.

The quantum spin Hall effect, predicted in 1971, was only shown experimentally in 2006 by Professor Laurens Molenkamp of the University of Würzburg, who used mercury telluride/cadmium telluride quantum wells at very low temperature. Theoretical physicists then designed several mercury telluride honeycomb structures, several of which appeared to have the properties they were looking for.

"At the moment Prof Molenkamp is the only expert working with mercury telluride. Although it is not yet possible to realise it experimentally, he expects the technology necessary will be available within a short time."

Author

Graham Pitcher

Source: www.newelectronics.co.uk

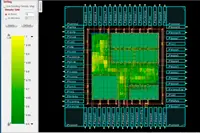

Cadence Design Systems has introduced the Innovus Implementation System, said to allow SoC developers to improve power, performance and area (PPA), while reducing time to market. According to the company, Innovus can improve PPA by up to 20% at advanced process nodes and is '10nm ready'.

Cadence Design Systems has introduced the Innovus Implementation System, said to allow SoC developers to improve power, performance and area (PPA), while reducing time to market. According to the company, Innovus can improve PPA by up to 20% at advanced process nodes and is '10nm ready'.

Key features of the package include:

• GigaPlace solver-based placement technology

• Advanced timing and power driven optimisation

• Concurrent clock and datapath optimisation

• Next generation slack driven routing with track aware timing optimisation

• Multi objective technology for global optimisation

Core algorithms have been upgraded with multithreading whilst a massively distributed parallel solution enables design blocks with 10million instances or larger. Multi scenario acceleration is said by Cadence to speed runtime, even with more multimode, multi corner scenarios.

"Customers have already started to employ the Innovus Implementation System to help achieve higher performance, lower power and minimised area to deliver designs to the market before the competition," said Anirudh Devgan, senior vice president of Cadence's Digital and Signoff Group. "Early customers are reporting significantly better PPA and a substantial speed up in turnaround time reduction versus competing solutions."

In a testimonial supplied by Cadence, Fares Bagh, vice president, hardware and architecture engineering with Freescale's Digital Networking Group, said: "We've tested the full Innovus Implementation System flow on some of our most congestion challenged 28nm networking IP blocks and have achieved excellent results while seeing significant throughput improvements

"The solution has enabled us to resolve our most difficult timing requirements and we anticipate that our deployment will allow us to grow our IP block sizes and accelerate SoC level design closure."

Key features of the package include:

• GigaPlace solver-based placement technology

• Advanced timing and power driven optimisation

• Concurrent clock and datapath optimisation

• Next generation slack driven routing with track aware timing optimisation

• Multi objective technology for global optimisation

Author

Graham Pitcher

Source: www.newelectronics.co.uk