5559ИН19У - КМОП-микросхема, содержащая две пары LVDS-передатчиков и приемников, оптимизированная для использования в высокоскоростных и низкопотребляющих системах передачи данных. За счет использования LVDS-технологии микросхема способна передавать данные со скоростью до 400 Мбит/с.

Передатчики 5559ИН19У принимают LVTTL/LVCMOS-сигналы и преобразуют их в LVDS-сигналы. Приемники получают LVDS-сигналы и преобразуют их в 3 В КМОП-сигналы. Буферы на LVDS-входах имеют схему помехозащищающего смещения, которая при плавающем входном сигнале устанавливает на выходах приемника высокий логический сигнал.

Если на входы En и nEn подать соответствующие логические сигналы, то выходы прибора перейдут в высокоимпедансное состояние. Активизируются и отключаются все приемники и передатчики прибора одновременно.

Таблица 1 описывает состояние выходов микросхемы в зависимости от значения сигналов на управляющих входах En и nEn.

Таблица 1

En | nEn | LVDS Out | LVCMOS Out |

L or Open | L or Open | OFF | OFF |

H | L or Open | ON | ON |

L or Open | H | OFF | OFF |

H | H | OFF | OFF |

L or open - низкий уровень или отсутствие сигнала, H - высокий уровень сигнала,

OFF - выключен, ON - включен.

ИС имеют сигнал отключения передатчиков (выходы с "третьим состоянием"), однополярное питание, встроенную защиту входов приемника от электрического смещения, состояния высокого импеданса на выходах LVDS при выключении питания и соответствуют стандарту TIA/EIA-644-ALVDS.

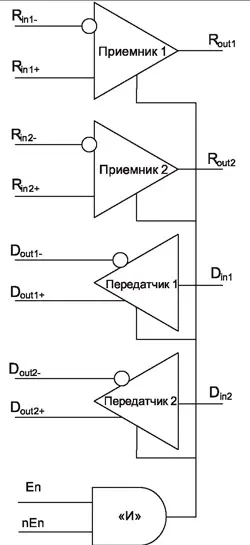

Структурная схема ИС представлена на рис. 1. Они выпускаются в металлокерамическом корпусе типа Н02.16-1В.

Рис. 1

LVDS-передатчики и приемники, прежде всего, предусмотрены для применения в несложных межблочных конфигурациях, как показано на рис. 1.

Данная конфигурация обеспечивает "чистую" подачу сигнала для ускорения работы передатчиков. Приемник подключается к передатчику через согласованный носитель, которым может быть стандартный кабель с витой парой или обычные дорожки на печатной плате. Обычно дифференциальный импеданс линии передачи составляет около 100 Ом.

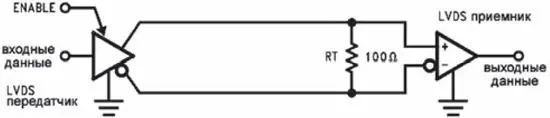

При подключении интерфейса LVDS "точка-точка" (рис. 2) согласующий резистор в 100 Ом располагается максимально близко к входным выводам приемника. Согласующий резистор преобразует выходной ток передатчика (токовый режим) в напряжение, которое определяется приемником.

Рис. 2.

Возможны и другие схемы включения, например, включение с несколькими приемниками. Использование выходов с тремя состояниями позволяет отключать выходы устройства, что способствует снижению потребления энергии при отсутствии передачи данных.

Приемник LVDS является высокоскоростным устройством, обладающим большим усилением, способным увеличивать небольшой дифференциальный сигнал (20 мВ) до КМОП логических уровней. Из-за большого усиления и жесткого порогового значения необходимо учитывать амплитуду помех на линии передачи.

Назначение выводов микросхемы приведено в табл. 2.

Таблица 2. Назначение выводов МС

Номер вывода | Обозначение вывода | Назначение вывода |

| 1 | Rout1 | Цифровой выход приемника 1-го канала, уровни LVCMOS |

2 | Din1 | Цифровой вход передатчика 1-го канала, уровни LVCMOS |

3 | Rin1- | Инверсный вход приемника 1-го канала, уровни LVDS |

4 | Rin1+ | Прямой вход приемника 1-го канала, уровни LVDS |

5 | Dout1- | Инверсный выход передатчика 1-го канала, уровни LVDS |

6 | Dout1+ | Прямой выход передатчика 1-го канала, уровни LVDS |

7 | Ucc | Напряжение питания |

8 | GND | Общий вывод |

9 | En | Прямой сигнал разрешения работы микросхемы |

10 | D out2+ | Прямой выход передатчика 2-го канала, уровни LVDS |

11 | Dout2- | Инверсный выход передатчика 2-го канала, уровни LVDS |

12 | RIN2+ | Прямой вход приемника 2-го канала, уровни LVDS |

13 | RIN2- | Инверсный вход приемника 2-го канала, уровни LVDS |

14 | DIN2 | Цифровой вход передатчика 2-го канала, уровни LVCMOS |

15 | nEN | Инверсный сигнал разрешения работы микросхемы |

16 | ROUL2 | Цифровой выход приемника 2-го канала, уровни LVCMOS |

Электрические параметры

Статические характеристики:

а) Цифровых входов LVCMOS (Din, nEn, En):

- Входной ток высокого уровня при UIN = Ucc: J|±10| мкА

- Входной ток низкого уровня при UIN = 0: J|±10| мкА

б) Передатчика LVDS (Dout+, Dout-):

- Дифференциальное выходное напряжение: 250...450 мВ

- Изменение дифференциального выходного напряжения при RL = 100 Ом (рис. 2): ≤ 35 мВ

- Напряжение смещения: 1,125...1,375 В

- Ток короткого замыкания при Din = Ucc, Dout+ = 0 или Din = 0, Dout = 0: ≤15 мА

- Дифференциальный ток короткого замыкания включен, Dout+ = Dout- = 0: ≤ 9 мА

- Входной ток утечки при Uсс = 0, Uout = 0,36 В: ≤|±20| мкА

- Входной ток утечки в "третьем состоянии": ≤ |±10| мкА

в) Приемника LVDS (Rin+, Rin-):

- Дифференциальное напряжение переключения в "1" при Uсм = 1,2 В; 0,05 В; 2,35 В: ≤ 35 мВ

- Дифференциальное напряжение переключения в "0": ≥ |-100| мВ

- Входной ток при Uсс = 3,6 В, Uin = 0: ≤ |±12| мкА при Uсс = 0, Uin = 0; 3,6 В: ≤ |±10| мкА

г) Приемника LVCMOS (Rout):

- Выходное напряжение высокого уровня при Iон = -0,4 мА UID = 200 мВ: ≥ 2,7 В

- Выходное напряжение низкого уровня при IOL = 2 мА, UID = 200 мВ: ≤ 0,25 мВ

- Входной ток утечки в "третьем состоянии" при Ucc = 3,6 В, Uout = 0 В, Ucc: ≤ |±10| мкА

- Ток потребления при En = 3,3 В: ≤ 35 мА

- Ток потребления с выходами в "третьем" состоянии при Еn = 0: ≤ 25 мА

Динамические параметры:

д) Передатчика LVDS (Dout+, Dout-1):

- Время задержки распространения сигнала от Din до Dout, RL = 100 Ом: ≤ 2 нс

- Разница времен задержки распространения сигнала между каналами при RL = 100 Ом: ≤ 0,5 нс

- Длительность фронта переключения сигнала при RL = 100 Ом: ≤ 1 нс

- Время задержки перехода в "третье" состояние при выключении при RL= 100 Ом: ≤ 3 нс

- Время задержки перехода из "третьего" состояния при включении при RL= 100 Ом: ≤ 6 нс

е) Приемника LVCMOS (Rout):

- Время задержки распространения сигнала от Rin до Rout: ≤ 3,5 нс

- Разница времен задержки распространения сигнала между каналами: ≤ 0,5 нс

- Длительность фронта переключения сигнала: ≤14 нс

- Время задержки перехода в "третье" состояние при выключении: ≤ 8 нс

- Время задержки перехода из "третьего" состояния при включении: ≤ 7 нс

Примечание:UID - входное дифференциальное напряжение на входах Rin+, Rin-.

Предельно допустимые и предельные режимы эксплуатации

• Напряжение питания: 3...3,6 В

- в пределах режима: ≤4 В

• Входное напряжение высокого уровня:

- на выводах Din, nEn, En: 2...Ucc, В

- в предельном режиме: Ucc + 0,3 В

• Входное напряжение низкого уровня:

- на выводах Din, nEn, En: 0...0,8 В

- в предельном режиме: ≥ |-0,3| В

• Значение статического электричества: ≥ 2 кВ

• Синфазное напряжение на выводах Rin+, Rin-: 0,05...3 В

- в предельном режиме: -0,3...+3 В

• Ток короткого замыкания на выходе Rout: ≤ 50 мА

• Частота функционирования: ≤ 200 МГц

• Температура окружающей среды: 5559ИН19У К5559ИН19У: -60...+125°С, К5559ИН19АУ: 0...70°С

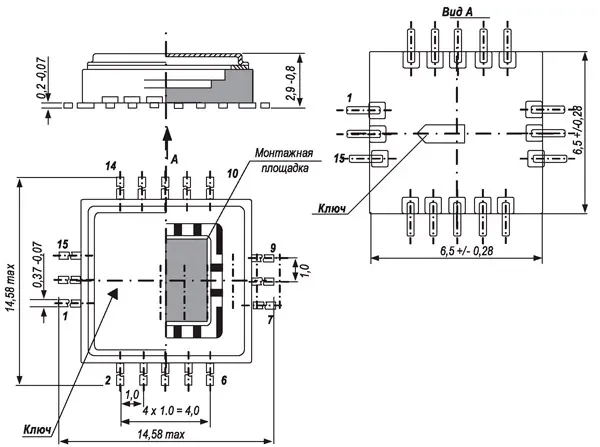

Рис. 3

Рекомендации по применению

На выводах питания необходимо использовать высокочастотные керамические конденсаторы емкостью 0,1 мкФ и 0,001 мкФ (лучше для поверхностного монтажа). Дополнительное использование развязывающих конденсаторов на печатной плате усиливает развязку. Для их подключения должны быть использованы многократные сквозные соединения. Полупроводниковый танталовый конденсатор емкостью 10 мкФ (35 В) или больше подключается к точке входа питания на печатной плате между источником питания и "землей". Согласующий резистор должен совпадать по значению с дифференциальным импедансом или сопротивлением линии передачи и составлять от 90 до 130 Ом. Обычно достаточно одного резистора со стороны приемника с точностью 1% и 2%.

ИС имеет два приемника и если необходим только один, то неиспользуемые входы другого необходимо оставлять неподключенными к заземлению или к другим источникам напряжения. Входной сигнал смещается с помощью повышающих или понижающих внутренних источников постоянного тока для установления высокого напряжения на выходе. Эта встроенная схема гарантирует стабильно высокий уровень выходного напряжения на неподключенных входах.

Маркировка: 5559ИН19У - ИН19; К555919У - КН19; К5559ИН19АУ - КИН19.

Автор: Анатолий Нефедов (г. Москва)

Источник: Ремонт и сервис