Общие сведения, технические характеристики и конструкция

ТВ шасси AZ1-A было разработано и внедрено в производство в 2008-2009 гг На основе этого шасси в течение 2008-2011 гг было выпущено большое количество моделей ЖК телевизоров c диагоналями панелей 22, 26, 32, и 40 дюймов для реализации в различных регионах мира (см. таблицу 1). За этот период шасси AZ1-A получило несколько ревизий плат, входящих в его состав, а также различные конструктивные и дизайнерские решения.

Таблица 1. Список моделей ТВ SONY на основе шасси AZ1-A

Модели ТВ | Год выпуска | пду | Регионы продаж |

KLV-22BX300, KLV-26BX300, KLV-32BX300 | 2009 | RM-019 | Иран, Индия, Россия. Индонезия, Малайзия, Новая Зеландия, Нигерия, Саудовская Аравия, Украина, Сингапур, ЮАР, Таиланд, Тунис, Филлипины |

KLV-40BX400 | 2009 | RM-019 | Иран, Россия, Индонезия, Малайзия, Нигерия, Саудовская Аравия, Украина, Сингапур, ЮАР, Индия, Таиланд |

KLV-22BX300/1, KLV-26BX300/1, KLV-32BX300/3, KLV-40BX400/3 | 2010 | RM-GA019 | Нигерия, Кувейт, Кения, Саудовская Аравия |

KLV-22BX301, KLV-26BX301, KLV-32BX301, KLV-40BX401 | 2011 | RM-GA019 | Россия |

KLV-22BX310, KLV-26BX310, KLV-32BX310 | 2011 | RM-GA019 | Нигерия, Кувейт, Кения |

Основные технические характеристики ТВ на шасси AZ1-A приведены в таблице 2.

Таблица 2. Основные технические характеристики ТВ на шасси AZ1-A

Характеристика | Описание | |||

Название модели | KLV-22BX300, KLV-22BX301 | KLV-26BX300, KLV-26BX301 | KLV-32BX300, KLV-32BX301 | KLV-40BX300, KLV-40BX301 |

Физическое разрешение ЖК панели, пикселов | 1366 х 768 | 1920 х 1080 | ||

Тип задней подсветки ЖК панелей | Люминесцентная (CCFL - Cold Cathode Luminescent Lamp) | |||

Система TB | B/G, I, D/K, M | |||

Принимаемые каналы | B/G: VHF: E2-E12/ UHF: E21-E69/ CATV: S01-S03, S1-S41 I: UHF: B21-B69/ CATV: S01-S03, S1-S41 D/K: VHF: C1-C12, R1-R12/ UHF: C13-C57, R21-R60/ CATV: S01-S03, S1-S41, Z1-Z39 M: VHF: A2-A13/ UHF: A14-A79/ CATV: A8-A2, A-W+4, W+6-W+84 | |||

Питание | Переменное напряжение 220...240 В, 50/60 Гц | |||

Выходная мощность УМЗЧ | 5 Вт х 2 канала | 8 Вт х 2 канала | 10 Вт х 2 канала | |

Потребляемая мощность | 50 Вт | 80 Вт | 115 Вт | 180 Вт |

Разъемы | ||||

Антенный вход | Коаксиальный, импеданс 75 Ом | |||

Компонентный вход (COMPONENT IN) | Разъемы типа Jack Поддерживаемые форматы: 1080p, 1080i, 720p, 576p, 576i, 480p, 480i Y: 1 Vp-p, 75 Ом, 0,3 В отрицательная синхронизация/PB/CB: 0,7 Vp-p, 75 Ом/PR/CR: 0,7 Vp-p, 75 Ом | |||

Интерфейс (HDMI IN 1, 2) | Видеоформаты: 1080/24p, 1080p, 1080i, 720p, 576p, 576i, 480p, 480i Аудиоформаты: двухканальный линейный PCM: 32, 44,1 и 48 кГц, 16, 20 и 24 бита Aналоговый аудиовход (разъем типа MINIjack) (только у HDMI IN 2) | |||

Вход для ПК (PC IN) | Вход ПК (D-sub 15-pin) и аудиовход типа MINIjack G: 0,7 Vp-p, 75 Ом, отрицательная синхронизация по зеленому/B: 0,7 Vp-p, 75 Ом/ R: 0,7 Vp-p, 75 Ом/HD: 1-5 Vp-p/VD: 1-5 Vp-p | |||

Интерфейс (USB) | USB 2.0 | |||

В дальнейшем описании шасси будут рассматриваться модели ТВ для российского рынка: KLV-22BX301, KLV-26BX301, KLV-32BX301, KLV-40BX401. Схемы соединений узлов и плат, входящих в состав шасси, приведены на рис. 1.

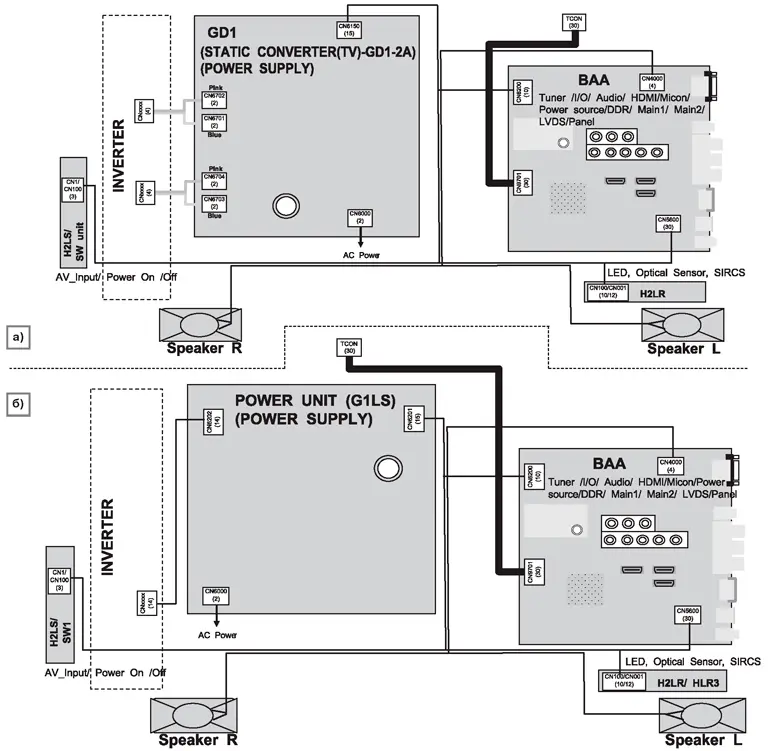

Рис. 1. Схемы соединений узлов и плат, входящих в состав шасси AZ1-A, где а - схема для модели KLV-22BX300, б - KLV-26BX300, в - KLV-32BX300, г - KLV-40BX300

В состав шасси AZ1-A входят следующие платы и узлы: - главная плата BAA (Tuner /I/O/ Audio/ HDMI/Micon/Power source/DDR/ Main1/ Main2/LVDS/Panel);

- плата панели управления H2LR (LED, Optical Sensor, SIRCS) (H2LR/HLR3 - для модели KLV-26BX300);

- плата DC/AC-конвертора питания CCFL задней подсветки ЖК панели INVERTER;

- плата блока питания GD1 (для модели KLV-22BX300), G1LS (KLV-26BX300), G2LE (KLV-32BX300) или G2HE (KLV-40BX300);

- плата НЧ входа и сетевого выключателя H2LS/SW1;

- плата TM BOARD (опция для некоторых моделей KLV-26BX300);

- динамические головки (2 шт.);

- ЖК панель (диагональ в зависимости от модели ТВ);

- детали корпуса и подставки. Как пример размещения всех вышеперечисленных составных частей шасси в корпусе ТВ, на рис. 2 (см. в архиве ниже) приведена схема разборки модели KLV-22BX300.

Блок-схема шасси

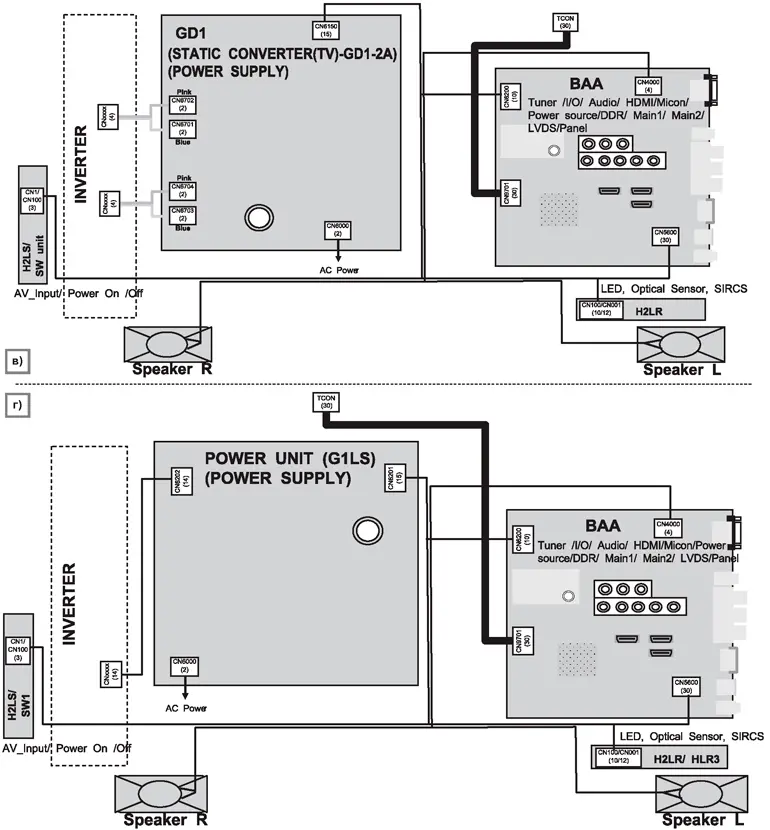

Блок-схема шасси AZ1-A приведена на рис. 1. Оно выполнено на основе ИМС MT5388 тайваньской фирмы MediaTek, более известной своими чипами для смартфонов. Эта микросхема представляет собой "систему на кристалле" SoC (System-on-a-Chip) - комбинацию цифрового ТВ декодера и управляющего микроконтроллера. ИМС MT5388 включает в себя следующие блоки:

- мультисистемный демодулятор;

- демультиплексор транспортного потока TS;

- MPEG-2-видеодекодер с высоким разрешением;

- аудиодекодер стандартов АС3/MPEG2;

- двухканальный LVDS-передатчик;

- мультисистемный (NTSC/PAL/ SECAM) ТВ декодер с гребенчатым 3D-фильтром NTSC/PAL;

- приемник сигналов интерфейса HDMI1.3;

- универсальные порты ввода/вывода;

- управляющий интерфейс I2C;

- 16-разрядный интерфейс оперативной памяти DDR2-SDRAM;

- интерфейс Flash-памяти;

- отладочный интерфейс JTAG (для внутрисхемного программирования ИМС);

- интерфейс USB и другие узлы.

ТВ сигнал с антенны поступает на вход гибридного тюнера (Tuner на рис. 3). Тюнер управляется по цифровой шине I2C ИМС MT5388. На выходе тюнера формируется дифференциальный сигнал 1-й ПЧ, который через полосовой фильтр SAW (38 МГц) поступает на блок цифрового декодера в составе ИМС. Демультиплексор транспортного потока TS выделяет из сигнала ПЧ цифровой сигнал TS, который поступает непосредственно на MPEG-2-декодер. Для работы MPEG-2-декодер в составе SoC использует два типа памяти - DDR2-SDRAM объемом 64/128 Мбайт и Flash-память объемом 64 Мбайт. Из сигнала TS декодер формирует цифровые сигналы изображения в стандарте ITU656 (интерфейс для передачи цифрового потока 4:2:2 YCBCR) и стереосигнал звукового сопровождения, которые обрабатываются различными узлами в составе ИМС. Кроме указанных цифровых сигналов на вход SoC может поступать цифровой сигнал с одного из двух входов HDMI1-HDMI2. Сигналы на этих входах представляют собой три пары дифференциальных сигналов данных D0-D3 и одну пару тактовых сигналов CLK. Вначале сигналы поступают на коммутатор в составе MT5388, а с его выхода выбранный пользователем сигнал подается на декодер HDMI, который преобразует дифференциальные сигналы в 8-разрядные коды. Затем этот цифровой сигнал обрабатывается SoC так же, как и сигнал с выхода декодера MPEG-2.

Рис. 3. Блок-схема и принципиальная электрическая схема шасси AZ1-A

ИМС SoC имеет и аналоговые входы, на которые подаются видеосигналы с аналоговых входов ТВ:

- с выхода гибридного тюнера;

- с разъемов видеовхода 1 (Video 1) композитный сигнал CVBS1;

- с разъемов видеовхода 2 (Video 2) композитный сигнал CVBS2;

- с разъемов видеовхода 3 компонентный сигнал YUV или композитный сигнал CVBS3;

- с вышеперечисленных разъемов звуковые стереосигналы L/R;

- сигналы PC_RGB, H, V c разъема для персонального компьютера PC.

Вся последующая обработка видео- и аудиосигналов, аналоговых или цифровых, выполняется ИМС MT5388. Выбранный пользователем аналоговый видеосигнал поступает на АЦП и преобразуется в цифровой сигнал с разрешением 1280 х 720p х 60 Гц. Все цифровые видеосигналы, имеющие другой формат, масштабируются в ИМС к этому разрешению.

Как уже отмечалось, для хранения промежуточных данных SoC использует динамическую память DDR2-SDRAM, а управляющие программы хранятся во Flash-памяти.

В результате обработки SoC MT5388 формирует цифровой видеосигнал, который подается на контроллер интерфейса LVDS в составе этой ИМС. В зависимости от диагоналей используемых ЖК панелей он может работать в одно-или двухканальном режимах - в первом случае для панелей с диагоналями 22, 26 и 32 дюйма с разрешением HD Ready (1366 х 752 пикселов), и во втором случае - для 40-дюймовых панелей с разрешением Full HD (1920 х 1080 пикселов). В одноканальном режиме интерфейс преобразует цифровой сигнал в 6 пар дифференциальных сигналов - 5 пар сигналов данных и одну пару тактовых сигналов. В двухканальном режиме количество пар сигналов удваивается. Кроме этих сигналов ИМС MT5388 формирует управляющие сигналы для контроля ЖК панели.

Как и в предыдущем случае, практически вся обработка звуковых сигналов происходит в ИМС MT5388. Из эфирного сигнала ПЧ в аналоговом тракте ИМС выделяется звуковой сигнал и поступает на коммутатор аналоговых сигналов звука. Сюда же подаются аналоговые звуковые сигналы с входов Video1-Video3. Выбранный пользователем сигнал (вход) оцифровывается и подается на цифровой звуковой процессор в составе ИМС. После соответствующей обработки цифровые сигналы стереозвука поступают на выход ИМС. Отсюда сигналы звука через фильтры нижних частот LPF поступают на внешний цифровой усилитель мощности типа TPA3110D2, а с его выходов - на динамические головки.

С отдельного выхода SoC звуковой сигнал подается на усилитель линейного выхода (наушников) AMP типа NJM2779.

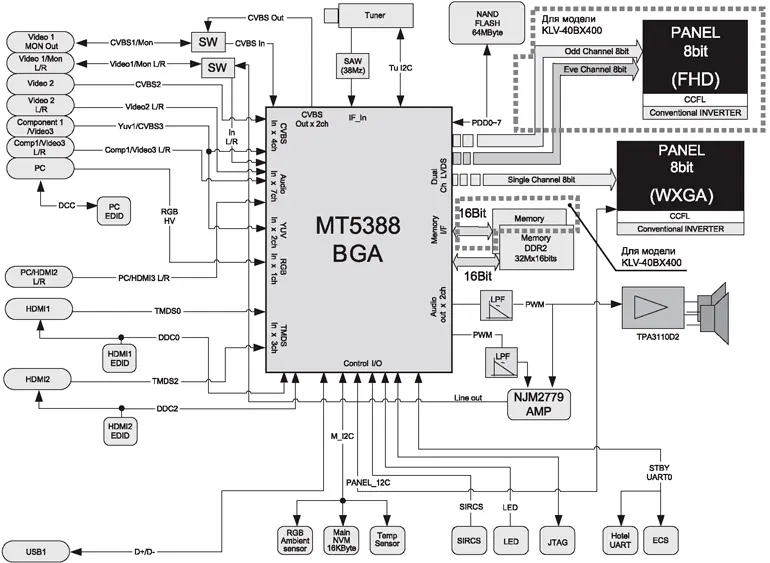

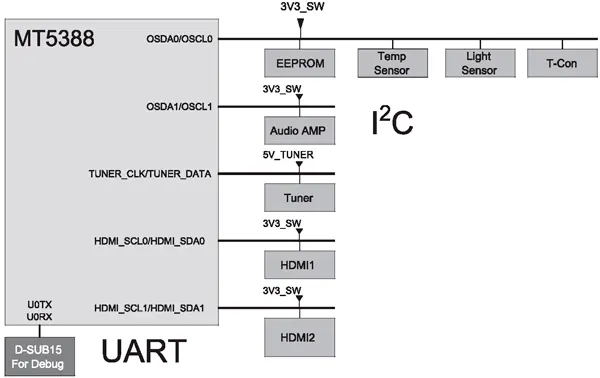

ИМС МТ5388 имеет 5 интерфейсов I2C (см. рис. 4). Одним из них ИМС соединена с главной микросхемой энергонезависимой памяти, сенсорами температуры, освещенности и контроллером ЖК панели T-Con. К остальным интерфейсам I2C подключены аудиоусилитель, гибридный тюнер и входы HDMI1/2.

Рис. 4. Схема подключения интерфейсов I2C MT5388 к шасси

ИМС MT5388 совмещает функции управляющего и дежурного микроконтроллеров. На эту ИМС постоянно подается дежурное напряжение 3,3 В от платы блока питания.

Есть 4 различных варианта платы блока питания, которые используются на шасси в зависимости от диагонали ЖК панели (см. выше).

В каждом варианте имеются две отдельных секции: дежурный источник питания и рабочий источник питания. В режиме ожидания (дежурный режим) постоянно задействован только дежурный источник. Он формирует постоянное стабилизированное напряжение 3,3 В для цепей, требующих питания, когда аппарат выключен, и постоянное напряжение 15 В для питания управляющих схем корректора коэффициента мощности (ККМ) и рабочего источника питания при включении.

После того как на плату питания поступает сигнал на включение от управляющего микроконтроллера главной платы, основной (рабочий) источник включается и формирует постоянные напряжения 12, 15 и 24 В для питания всех узлов шасси, включая инвертор. Инвертор конвертирует постоянное напряжение 24 В в переменное высокое напряжение (более 1000 В и током 5...10 мА на канал) для питания люминесцентных ламп подсветки. От главной платы на инвертор поступают управляющие сигналы для его включения и регулировки яркости подсветки (димминга).

На шасси имеются сервисные разъемы, на которые выведены сигналы последовательных интерфейсов UART и JTAG. Они используются в заводских условиях или сервисном центре для сервисных регулировок, записи/чтения сервисных данных, а также перепрограммирования управляющего ПО.

Для более подробного ознакомления с шасси AZ1-A можно обратиться к его принципиальной электрической схеме, приведенной здесь. В этом архиве отсутствуют схемы блоков питания, они будут рассмотрены в отдельной статье.

Принципиальная электрическая схема и схема разборки телевизоров SONY BRAVIA на основе шасси AZ1-A находятся здесь.

Продолжени следует

Автор: Николай Елагин (г. Зеленоград)

Источник: Ремонт и сервис