Особенности построения и характеристики перечисленных домашних кинотеатров (ДК) были рассмотрены в предыдущей статье автора [1]. Усилительные блоки всех перечисленных ДК выполнены практически по одной схеме, самой сложной является модель "LH-SW5100", основное отличие которой - использование радиоканала для подачи звуковых сигналов на тыловые акустические системы и сабвуфер. В схемном и конструктивном отношениях это отличие заключается в использовании дополнительных блоков и плат. Структурная схема и схема соединений усилительных блоков рассматриваемых систем ДК приведены в [1]. На рис. 1 приведена электрическая принципиальная схема узла входов/выходов модели "LH-T1000" (I/O SECTION), находящегося в составе главной платы усилительных блоков (УБ).

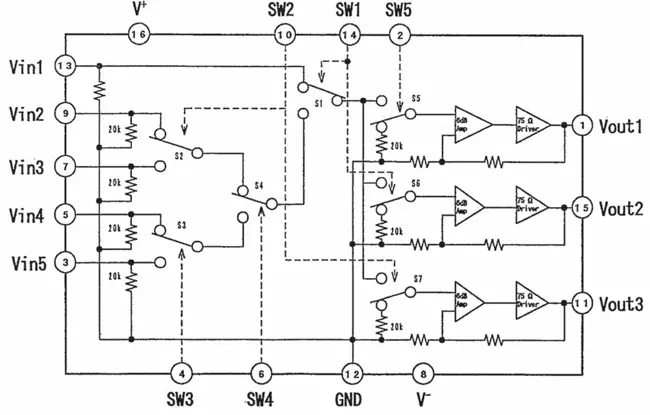

Коммутатор входных видеосигналов УБ выполнен на микросхеме IC601 типа NJM2296M фирмы New Japan Radio (JRC). Эта ИМС коммутирует композитные видеосигналы входов VIDEO1 IN, VIDEO2 IN линейки разъемов JK60A/V на задней панели УБ и композитный видеосигнал от секции DAP section на выходы VIDEO1 OUT, MONITOR OUT и контакт 19 разъема JK602. Напряжение питания +5 В подается на выв. 16 IC601 через дроссель L601, а напряжение -5 В - на выв. 8 через дроссель L602 и резистор R602, величину напряжения задает стабилитрон ZD601. Микросхема NJM2296M является коммутатором композитных видеосигналов типа 5 х 3 (5 входов, 3 выхода). Напряжение питания микросхемы - ±(4,5...6,5) В, напряжения управляющих сигналов на выводах SW1-SW5: лог. "0" соответствует уровню (0...1) В, а лог. "1" - уровню (3...5) В. Структура микросхемы приведена на рис. 2. В рассматриваемом УБ функции микросхемы задействованы не полностью, это позволяет использовать резервные входы (Vin1, Vin2) микросхемы при возникновении неисправностей в отдельных каналах.

Рис. 2. Структура микросхемы NJM2296M

Управление коммутатором IC601 осуществляется по цепям 2296_SW3, 2296_SW4 от системы управления (секция U-COM SECTION или MICOM SECTION). Проверку прохождения видеосигналов через коммутатор производят на соответствующих контактах соединителей JK60A/V, JK602, размах испытательных сигналов цветных полос на холостом ходу должен быть равен 2 В, на нагрузке 75 Ом - 1 В, не должно быть искажений (завалов фронтов) синхроимпульсов.

На микросхемах IC501-IC503 типа NJM4580M выполнены формирователи звуковых сигналов БУ Сдвоенные ОУ NJM4580 фирмы JRC отличаются низким уровнем шумов (0,8 мкВ), малыми искажениями (0,0005%), широким диапазоном частот (15 МГц), высокой скоростью нарастания выходного напряжения (5 В/мкс), напряжение питания равно ±(2...18) В. Микросхемы выпускаются в корпусах DIP8, SIP8, EMP8, SSOP8, DMP8. На входы ОУ IC501, включенного по схеме интегратора (ФНЧ), подаются дифференциальные ШИМ сигналы левого и правого фронтальных каналов от звукового процессора DAP (DAP Section), на входы IC502 - ШИМ сигналы канала сабвуфера, на входы IC503 - ШИМ сигналы канала головных телефонов. Выделенные интеграторами звуковые сигналы подаются на контакты разъема JK60A и на систему управления по цепям H/P-L, H/PR. Напряжение питания ±12 В ОУ от импульсного источника питания (SMPS SECTION) подается на выв. 4, 8 IC501-IC503 через отдельные RC-фильтры.

Основные преобразования звуковых и импульсных сигналов в усилительном блоке осуществляет цифровой звуковой процессор DAP (DSP), его принципиальная электрическая схема приведена на рис. 3 (см. архив). Основой DAP является БИС IC301 типа PS9818 фирмы PULSUS TECHNOLOGIES, представляющая собой 8-канальный звуковой процессор, предназначенный для цифровых усилителей звуковых частот (DDX и других типов). Кроме рассматриваемых систем ДК микросхема применяется также в других системах фирм LG и SAMSUNG, в частности:

- ДК LG: "HTC-S5100", "DA-T5620", "FA-D5000", "XCH-6550TW", "XH-T755TK;

- ДК SAMSUNG: "SPS-3510", "HT-DS600", "HT-AS600T", "HT-DS1000T", "CHT-W7200T", "HT-TP3".

Отметим некоторые характеристики и возможности микросхемы PS9818:

- 2 последовательных порта для 8-канальных систем (7.1 Channels);

- поддержка частот дискретизации в диапазоне (32...192) кГ ц;

- 2-канальный ШИМ-выход на головные телефоны;

- динамический диапазон 105 дБ;

- программируемый 4-полосный эквалайзер в каждом канале;

- управления по шинам I2С, SPI.

Преобразование внешних звуковых сигналов и сигналов тюнера в цифровую форму осуществляет дельта-сигма АЦП IC201 типа AK5365 фирмы Asahi Kasei Microsystems (AKM). Перечислим некоторые характеристики и возможности преобразователя:

- дискретизация 24 разряда, частоты дискретизации (32...96) кГц;

- 5-канальный стереоселектор входных сигналов;

- входной усилитель с программируемым коэффициентом усиления (PGA) и авторегулировкой уровня (ALC);

- цифровой ФВЧ (HPF) и цифровой аттенюатор (DATT);

- выходные звуковые интерфейсы 24 bit MSB justified, I2S;

- интерфейсы управления I2C и 3-проводной последовательный μP-интерфейс;

- динамический диапазон и отношение сигнал/шум 103 дБ.

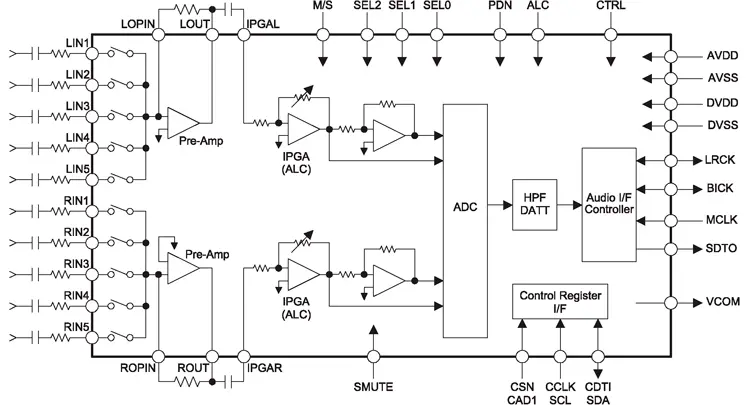

Рис. 4. Структура АЦП AK5365

Структура АЦП AK5365 приведена на рис. 4, в состав микросхемы входят:

- Pre-amp, предварительные интегрирующие усилители;

- IPGA (ALC), усилители с программируемым коэффициентом усиления и автоматической регулировкой уровня;

- ADC, сигма-дельта АЦП, HPF DATT - ФВЧ и цифровой аттенюатор;

- Audio I/F Controller, контроллер звуковых интерфейсов

- Control Register I/F, контроллер управляющих интерфейсов.

Назначение основных функциональных выводов микросхемы AK5365 приведено в таблице 1.

Таблица 1. Назначение основных функциональных выводов микросхемы AK5365

Номер вывода | Обозначение | Назначение |

1, 3, 5, 7, 9 | LIN5-LIN1 | Аналоговые входы левого канала |

12, 13 | IPGAL, IPGAR | Входы программируемых усилителей левого и правого каналов |

16 | AVDD | Напряжение питания аналоговых узлов (4,75...5,25) В |

17 | AVSS | Корпус аналоговых узлов |

19 | DVSS | Корпус цифровых узлов |

20 | DVDD | Напряжение питания цифровых узлов (3...5,25) В |

21 | SDTO | Выход данных звукового интерфейса |

22 | BICK | Выход тактовых сигналов звукового интерфейса |

23 | LRCK | Выход канальных тактовых сигналов |

24 | MCLK | Вход системных тактовых сигналов (master clock) |

26 | ALC | Вход включения режима автоматической регулировки уровня (вкл. лог. "1") |

28-30 | SEL0-SEL2 | Входы управления входными коммутаторами |

31-33 | CSN/CAD1, CCLK/SCL, CDTI/SDA | Входы интерфейсов управления 3-Wire, I20 |

34 | CTRL | Вход переключения интерфейсов управления, лог. "1" - I2С, лог. "0" - 3-wire |

35 | M/S | Вход переключения режимов ведущий/ведомый (master/slave) |

36, 38, 40, 42, 44 | RIN1-RIN5 | Аналоговые входы правого канала |

На микросхеме IC202 типа AK4117 фирмы АКМ выполнен приемник цифровых звуковых сигналов S/PDIF, AES/EBU с оптического и коаксиального цифровых звуковых входов. Перечислим основные параметры и возможности микросхемы.

- входные последовательные интерфейсы AES3, IEC60958, S/PDIF, EIAJ CP1201;

- диапазон тактовых частот (32...192) кГц;

- автоматическое определение типов цифровых потоков и частот дискретизации;

- выходные звуковые интерфейсы Left justified, Right justified, I2S (16, 18, 20, 24 разряда);

- 4-проводной μР-интерфейс управления;

- напряжение питания 2,7...3,6 В.

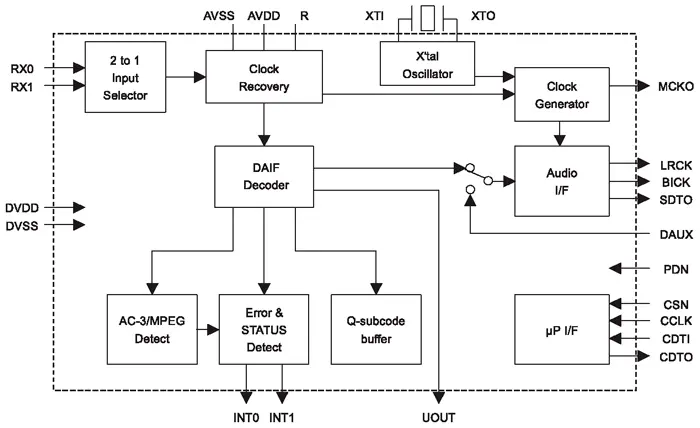

Архитектура микросхемы AK4117 приведена на рис. 5. В ее состав входят: входной селектор (2 to 1 input selector); регенератор тактовых частот (Clock Recovery); декодер звуковых последовательных интерфейсов (DAIF Decoder); детектор цифровых потоков (AC3/MPEG Detec); детектор ошибок и статуса (Error & STATUS Detect); буфер субкода (Q-subcode buffer); кварцевый генератор (Xtal Oscillator); тактовый генератор (Clock Generator); выходной звуковой интерфейс (Audio I/F); интерфейс управления (μP I/F). Назначение основных функциональных выводов микросхемы приведено в таблице 2.

Рис. 5. Архитектура микросхемы AK4117

Таблица 2. Назначение основных функциональных выводов микросхемы AK4117

Номер вывода | Обозначение | Назначение |

2, 6 | AVDD, DVDD) | Напряжения питания аналоговых и цифровых узлов |

3, 5 | RX1, RX0) | Входы каналов 1, 0 |

8, 9 | XTI, XTO | Выводы для подключения кварцевого резонатора |

10 | LRCK) | Выход канальных тактовых импульсов |

11 | BICK) | Выход тактовых импульсов звукового интерфейса |

12 | SDTO | Выход данных звукового интерфейса |

14 | MCKO | Выход системных тактовых импульсов |

17 | CDTO | Выход данных интерфейса управления |

18 | CDTI | Вход данных интерфейса управления |

19 | CCLK | Вход тактовых импульсов интерфейса управления |

При возникновении неисправностей в DAP можно рекомендовать следующий порядок их поиска: проверка прохождения напряжений питания, сигналов управления, тактовых сигналов, проверка звуковых интерфейсов, проверка прохождения внешних цифровых и аналоговых сигналов.

Цепь питания +3,3 В от импульсного источника питания (SMPS SECTION см. [1]), проверяются элементы L201, L203, L204, L206, L209, L302-L307, L309, R323, R324, R325, D300. После диода D300 напряжение уменьшается до 2,5 В. Проверку целостности печатных проводников и качество паянных соединений можно ограничить измерением напряжений на соответствующих выводах микросхем:

- цепь 3,3 В: выв. 10, 13, 22, 29, 39, 47, 56, 65, 72, 82, 83, 87, 91 IC301;

- цепь 2,5 В: выв. 3, 5, 6, 13, 34, 42, 66, 80, 91 IC301, выв. 20, 26 IC201, выв. 2, 7 IC202, выв. 20 IC203;

- цепь +5 В от ИИП, проверяются L208 и напряжение на выв. 16 IC201.

Все сигналы управления DAP и другими узлами УБ формирует система управления (СУ), ее принципиальная электрическая схема (MICOM SECTION) приведена на рис. 6. Система управления распложена на главной плате УБ. Ее основа - микропроцессор IC101 типа LC876764 фирмы SANYO.

Микросхема IC301 управляется по стандартной шине I2C, тактовые сигналы SCLK и сигналы данных SDI с выв. 85 и 91 микропроцессора IC101 (рис. 6) поступают на выв. 79, 78 микросхемы IC301 (рис. 3).

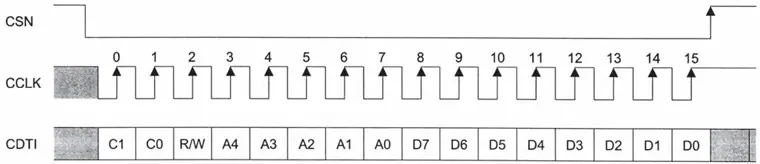

Для управления АЦП IC201 и цифровым приемником IC202 используется последовательный интерфейс 3-wire pP interface, структура которого приведена на рис. 7 (обозначения шин соответствуют рис. 4). Шина управления CSN (см. рис. 7) определяет режимы записи/считывания, информация записывается в регистры АЦП при уровне лог "0". При уровне лог. "1" записанная информация сохраняется в регистрах до прихода следующего лог. "0". Тактовая шина CCLK обеспечивает синхронизацию записи/считывания информации с шины данных CDTI. Синхронизация осуществляется по передним фронтам тактовых импульсов, максимальная частота следования которых не должна превышать 5 МГц (для AK5365). Шина данных CDTI содержит 16 разрядов: для режима 3-wire pP разряды адреса чипа зафиксированы - С1=1, С0=0; в разряде R/W (считывание/запись) зафиксирована лог "1" (запись); разряды А4-А0 являются адресами регистра; данные содержатся в разрядах D7-D0.

Рис. 7. Временные диаграммы сигналов CSN, CCLK и CDTI

Импульсы управления CSN (рис. 7) с выв. 22 микропроцессора IC101 (рис. 6) поступают на выв. 33 микросхемы IC201 (рис. 3). Тактовые импульсы CCLK с выв. 86 IC101 поступают на выв. 32 IC201 и выв. 19 IC202. Сигналы данных CDTI с выв. 88 IC101 поступают на выв. 31 IC201 и выв. 18 IC202.

Отдельные импульсы управления с вывода 24 IC101 поступают на выв. 20 IC202, это позволяет разделять по времени управление микросхемами IC201, IC202. Импульсы на всех шинах должны иметь размах не менее 3 В, измерения следует проводить ВЧ пробником с малой входной емкостью.

АЦП IC201 работает в ведомом режиме (задается лог. "0" на выв. 35), системные тактовые импульсы MCLK на выв. 24 поступают с выв. 14 микросхемы IC202, частота повторения импульсов 12,288 МГц, это соответствует режиму 256fs (при частоте дискретизации fs=48 кГц).

Проверку звуковых интерфейсов можно проводить в различных режимах работы УБ: воспроизведение CD/DVD, прием сигналов тюнера, работа от внешних аналоговых и цифровых источников. Независимо от режимов работы всегда задействован блок MPEG-модуля DVD (см. структурную схему УБ в [1]). Рассмотрим функционирование УБ при работе от аналоговых источников звуковых сигналов, которые можно подать на внешние входы VIDEO1 IN L/R, VIDEO2 IN L/R или SCART (рис. 1). Перед подачей на АЦП эти сигналы проходят через ФНЧ, например, в канале VIDEO1 IN L это элементы FB503, R505, R507, C506, отфильтрованные от ВЧ составляющих звуковые сигналы поступают на выводы LIN2-LIN4, RIN2-RIN4 микросхемы IC201 (рис. 3). Сигналы от тюнера поступают на выводы LIN1/RIN1. Коммутация каналов в микросхеме АК5365 может осуществляться последовательным кодом системы управления или параллельным 3разрядным кодом на выводах SEL0, SEL1, SEL2. В рассматриваемых УБ выбран первый способ (выв. 28, 29, 30 микросхемы IC201 заземлены).

Преобразованные в цифровую форму звуковой сигнал SDTO с выв. 21 АЦП поступает на выв. 13 (DAUX) микросхемы IC202, в которой он коммутируется на выход звукового интерфейса (Audio I/F. рис.7) и с выв. 12 подается на модуль DVD через контакт 10 разъема PN201 по цепи A_SPDATA. При работе УБ с цифровых (оптического или коаксиального) входов по этой же цепи проходит сигнал данных от цифрового приемника IC202.

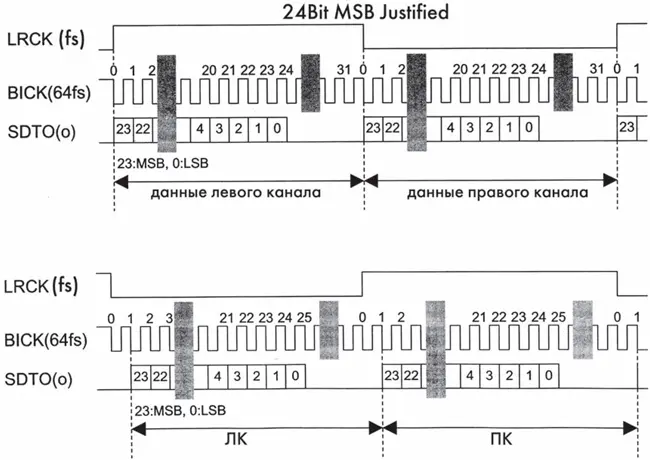

Тактовый сигнал BICK и канальный тактовый сигнал LRCK снимаются с выв. 11, 10 микросхемы IC202 и подаются на соответствующие входы АЦП (выв. 22, 23 IC201), работающего в ведомом режиме и на блок MPEG-модуля DVD через контакты 12, 11 разъема PN201 по цепям A_SPBCLK, A_SPLRCK. АЦП АК5365 обеспечивает работу с двумя форматами звуковых данных - I2S и 24 bit MSB Justified. В рассматриваемых УБ АЦП работает в последнем формате (формат задается лог. "0" на выв. 34 CTRL), временные диаграммы соответствующих сигналов приведены на рис. 8.

В формате MSB Justified при высоком уровне сигнала LRCK проходят данные SDTO левого канала, при низком - правого. Выравнивание, то есть согласование начала пакета данных SDTO с фронтами сигнала LRCK, производится по разряду MSB (старший разряд), в данном случае это 24-й разряд (№23 на диаграмме) и называется левым выравниванием (Left Justified). При частотах дискретизации и сигнала LRCK 48 кГц частота тактового сигнала BICK составляет 3,072 МГц (режим 64fs) или 2,304 МГц (режим 48fs). На нижней диаграмме рис. 8 показаны соотношения формата I2S (Inter Integrated Circuits Sound) - двунаправленная асинхронная шина с последовательной передачей данных внутри одного устройства. Пакеты данных левого канала в этом формате проходят при низком уровне сигнала LRCK и не привязаны к нему по фазе.

Рис. 8. Временные диаграммы звуковых и тактовых сигналов

Разъем PN201 через шлейф связан с разъемом PDA02 на плате модуля DVD, нумерация контактов и обозначения цепей одинаковы. Принципиальная электрическая схема блока MPEG-модуля DVD приведена на рис. 9, блок базируется на БИС IC501 MT1379 фирмы MEDIATEK (Тайвань). Рассмотренные выше сигналы по цепям A_SPDATA, A_SPMCLK, A_SPLRCK, A_SPBCK поступают на внутренний коммутатор БИС через выв. 181, 180, 183, 184. Выходные сигналы БИС ALRCK, ABCK, ASDAT0, ASDAT1, ASDAT2, ASDAT3 (пакеты данных левого и правого фронтальных каналов, центрального, левого и правого тыловых каналов и канала сабвуфера) снимаются с выв. 149, 148, 154-157. Эти сигналы приходят обратно на секцию DAP через разъем PN200 (рис. 3) и подаются на микросхему IC203 типа 74VHC244 фирмы FAIRCHILD. Микросхема является 8-канальным буферным драйвером с тремя состояниями выходов. Микросхема характеризуется высоким быстродействием (задержка распространения не превышает 5 нс при Uпит.=5 В), нечувствительностью к шуму (уровень до 28% от напряжения питания) и малым током потребления, не более 4 мкА.

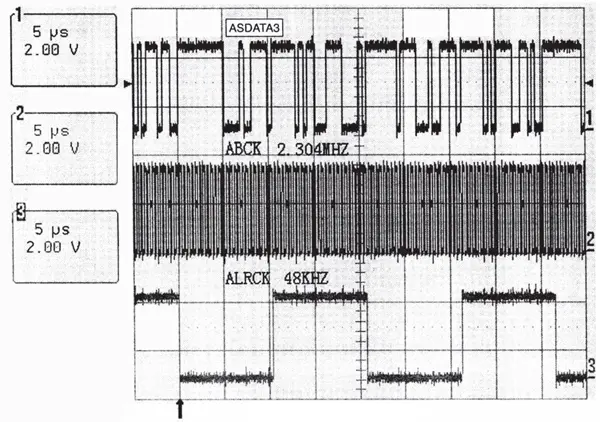

Сформированные и очищенные от шума сигналы снимаются с выв. 3, 5, 7, 9, 12, 14 микросхемы IC203 и подаются для преобразования в ШИМ сигналы на процессор DAP IC301 (выв. 20, 19, 23, 24, 25, 26 соответственно). Проверку прохождения цифровых звуковых сигналов по трактам УБ рекомендуется начинать с контроля сигналов звукового интерфейса на вышеперечисленных выводах процессора DAP IC301 в режиме воспроизведения CD/DVD, ориентируясь при этом на временные диаграммы рис. 8. При наличии цифрового осциллографа можно ориентироваться на рис. 10, на котором показаны осциллограммы сигналов ADATA3, BCLK (режим 48fs), LRCK, их удобно наблюдать на контактах 13, 8, 9 разъема PN200.

Рис. 10. Осциллограммы сигналов ADATA3, BCLK (режим 48fs), LRCK

Выходные ШИМ сигналы процессора DAP контролируют на плате секции усилителей (AMP SEC-TION)[1] и на плате входов/выходов (рис. 1).

Диагностику неисправностей системы управления (рис. 6) следует начинать с проверки прохождения напряжений питания от секции импульсного источника питания (SMPS SECTION) на выводы микропроцессора IC101,контакты разъема PN101 и на стабилизатор напряжения +9 В для питания тюнера, выполненный на элементах L103, R146, R150-R153, ZD100 (стабилитрон на напряжение 9,1 В).

Принципиальные электрические схемы моделей LH-6430, 6530, SW5100 могут иметь незначительные отличия от вышеприведенных схем модели LH-T1000.

Все недостающие схемы и рисунки можно скачать здесь.

Литература

1. Петропавловский Ю."Комплекты домашних кинотеатров фирмы LG Electronics с усилителями класса DDX", Ремонт & Сервис, 2009, №2.

Автор: Юрий Петропавловский (г. Таганрог)

Источник: Ремонт и сервис