Рассмотрим фрагмент принципиальной схемы основной платы с МП, который приведен на рис. 7 (см. в архиве ниже).

С входного интерфейса VGA на выв. 20, 21, 18, 19, 15, 16 МП U401 типа NT68660UFG/A фирмы NOVATEK подаются компонентные сигналы основных цветов R0±, G0±, B0±, на выв. 17 - сигнал опознавания SOG_DET, а на выв. 25, 26 - сигналы синхронизации AHS0, AVS0.

С входного интерфейса DVI на выв. 5, 6, 3, 4, 1, 2, 7, 8 микропроцессора подаются цифровые сигналы RX0±, RX1±, RX2±, RXС±.

В МП производится выбор и преобразование приходящих сигналов и формирование сигналов LVDS для их подачи на интерфейс ЖК панели.

Через выв. 85-89 МП связан с микросхемой последовательной Flash-памяти U402 типа MX25L2026DM1I фирмы MACRONIX International (объем 2 Мб) или типа Pm25LD020C фирмы FLASH Superior Endurance and Performance. Показанная на рисунке микросхема памяти U403 не используется.

На выв. 82, 83 МП поступают сигналы KEY1, KEY2 с платы клавиатуры управления, на выв. 90 - сигнал включения POWER.

С выв. 84, 99 МП подаются сигналы индикации LED1, LED2. В некоторых моделях сигналы индикации на светодиоды подаются через транзисторы Q401, Q402.

Сигналы включения (on_ BACKLIGHT) и выключения (Adj_ BACKLIGHT) задней подсветки подаются с выв. 79, 76 МП соответственно, сигнал включения/выклю-чения ЖК панели подается с выв. 42 МП.

С выв. 80, 81 микропроцессора подаются сигналы опознавания (Audio_DET) и включения (Audio_ EN) звука.

Кварцевый резонатор Х401 подключен между выв. 93 и 94 МП.

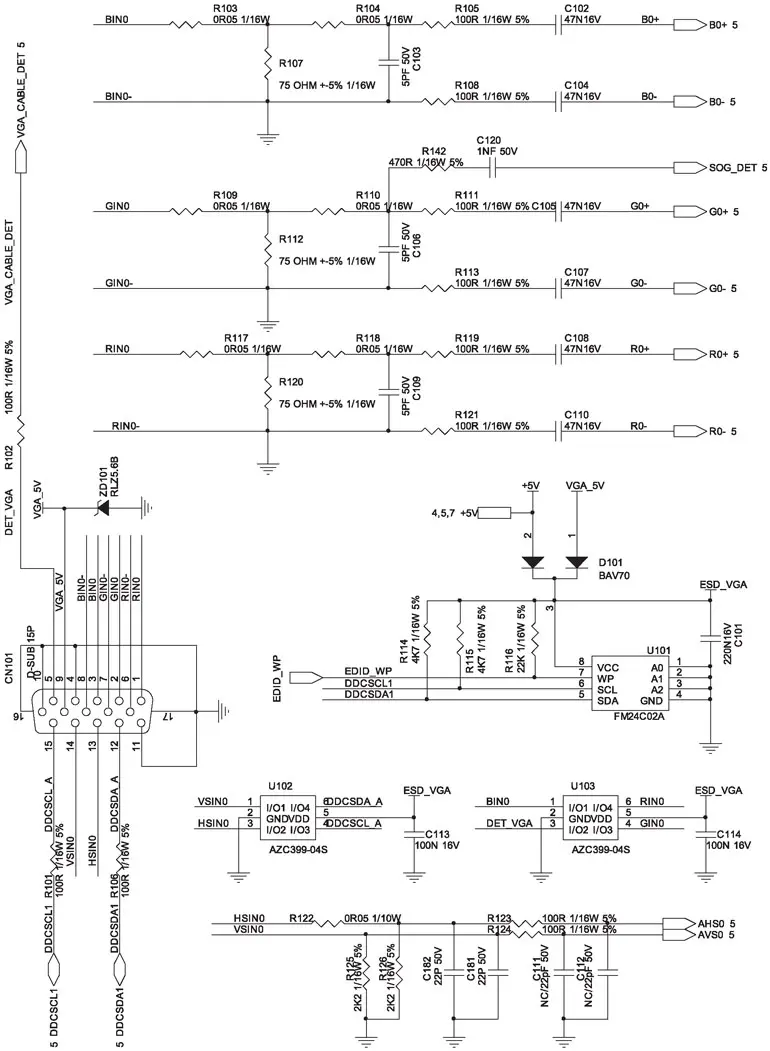

Фрагмент принципиальной схемы основной платы с входным интерфейсом VGA (D-SUB) представлен на рис. 8.

Рис. 8. Фрагмент принципиальной схемы основной платы с входным интерфейсом VGA (D-SUB)

Входные сигналы RIN0, RIN0-, GIN0, GIN0-, BIN0, BIN0-, HSIN0, VSIN0 подаются через контакты 1, 6, 2, 7, 3, 8, 13, 14 разъема CN101 соответственно и преобразуются в уже упомянутые сигналы R0±, G0±, B0± и SOG_DET, AHS0, AVS0, которые подаются на МП U401.

Сигнал опознавания DET_VGA (VGA_CABLE_DET) с контакта 5 разъема CN101 через показанный на рис. 7 (внизу слева) сумматор подается на выв. 36 МП.

Служебные сигналы цифровой шины управления DDC SDA1, DDC SCL1 подаются с контактов 12, 15 разъема CN101 на выв. 28, 27 МП U401 (см. рис. 7) и на выв. 5, 6 микросхемы последовательной памяти EEPROM U101 типа FM24C02A фирмы Fairchild Semiconductor. На выв. 8 этой микросхемы подается одновременно два напряжения питания: VGA_5V и +5V. При отключении кабеля VGA микросхема памяти продолжает работать от напряжения +5V. Для активизации микросхемы на ее выв. 7 подается сигнал EDID_WP с выв. 34 МП U401 (см. рис. 7).

На схеме показаны микросхемы U102 и U103 типа AZC 399-04S фирмы Amazing Microelectronic Corp., выполняющие функции защиты от электростатических разрядов (ESD). Они представляют собой сборки полупроводниковых диодов и стабилитронов, подключенных к сигнальным цепям.

Фрагмент принципиальной схемы основной платы с входным интерфейсом DVI представлен на рис. 9 (см. в архиве ниже).

Входные сигналы DAT0±, DAT1±, DAT2±, DCLK± подаются через контакты 18, 17, 10, 9, 2, 1, 23, 24 разъема CN102 соответственно и преобразуются в уже упомянутые сигналы RX0±, RX1±, RX2±, RXC±, которые подаются на МП U401.

Служебные сигналы цифровой шины управления DDC SDA2, DDC SCL2 подаются с контактов 7, 6 разъема CN102 на выв. 98, 97 МП U401 (см. рис. 7) и на выв. 5, 6 микросхемы последовательной памяти EEPROM U105 того же типа и той же фирмы, что и микросхема U101 интерфейса VGA. Как уже было показано выше, для активизации микросхемы на ее выв. 7 подается сигнал EDID_WP с выв. 34 МП U401.

Сигнал опознавания DET_ DVI (DVI _CABLE_DET) с контакта 15 разъема CN102 через уже упомянутый сумматор подается на выв. 36 микропроцессора.

Как и в интерфейсе VGA, здесь используются микросхемы защиты U104, U106 и U107 того же типа и той же фирмы, что и микросхемы U102 и U103.

Фрагмент принципиальной схемы основной платы с выходными разъемами LVDS приведен на рис. 10 (см. в архиве ниже).

С выв. 61, 60, 59, 58, 57, 56, 53, 52, 55, 54 микропроцессора U401 дифференциальные LVDS-сигналы LVA0M, LVA0P, LVA1M, LVA1P, LVA2M, LVA2P, LVA3M, LVA3P, LVACKM, LVACKP поступают на контакты 12, 13, 15, 16, 18, 19, 22, 23, 20, 21 разъема CN408 соответственно, а с выв. 72, 71, 70, 69, 68, 67, 64, 63, 66, 65 LVDS-сигналы LVB0M, LVB0P, LVB1M, LVB1P, LVB2M, LVB2P, LVB3M, LVB3P, LVBCKM, LVBCKP поступают на контакты 1-6, 10, 11, 8, 9 соответственно, откуда все они подаются на интерфейс ЖК панели.

Напряжение питания VLCD подается на панель через контакты 28-30 разъема.

Схемы, упомянутые в статье можно найти здесь.

Продолжение следует

Автор: Геннадий Романов (г. Москва)

Источник: Ремонт и сервис