На конференции International Solid-State Circuits Conference 2026 (ISSCC 2026), прошедшей 15–19 февраля в Сан-Франциско, компания Renesas Electronics анонсировала ряд значимых разработок для эпохи программно-определяемых автомобилей (SDV). В центре внимания — три новые технологии SoC для автомобильных мультидоменных электронных блоков управления (ЭБУ) и конфигурируемая архитектура троичной адресуемой по содержимому памяти (TCAM), реализованная на 3-нм техпроцессе FinFET.

Чиплетная архитектура с поддержкой функциональной безопасности ASIL D между кристаллами

Одна из ключевых задач при создании автомобильных SoC нового поколения — обеспечение функциональной безопасности в чиплетных конфигурациях, где несколько кристаллов обмениваются данными через высокоскоростные интерфейсы. Renesas решила эту проблему, разработав собственную архитектуру на базе отраслевого стандарта UCIe с механизмом контроля доступа на основе RegionID.

Стандартные реализации UCIe не передают RegionID между чиплетами. Renesas устранила это ограничение, отображая RegionID в адресное пространство, кодируя их в UCIe-регион и передавая между кристаллами. Такой подход позволяет блокам управления памятью и ядрам реального времени контролировать доступ к ресурсам в рамках чиплетной конфигурации и обеспечивать независимость компонентов (Freedom from Interference, FFI) в соответствии с требованиями ASIL D. Тестирование подтвердило, что интерфейс UCIe обеспечивает скорость передачи данных 51,2 ГБ/с — вблизи практического предела для внутрикристальной связи.

Качество обработки данных ИИ и бездефектное управление тактированием

По мере роста роли нейронных процессоров (NPU) в автомобильных SoC их площадь увеличилась примерно в 1,5 раза по сравнению с предыдущим поколением, что создаёт новые сложности при распределении тактового сигнала. Renesas решила эту задачу, встроив тестовые цепи непосредственно в иерархическую структуру генератора тактовых импульсов (CPG) и объединив пути пользовательского и тестового тактирования.

В режиме тестирования CPG верхнего и нижнего уровней синхронизируются с единым источником тактового сигнала, обеспечивая согласованную фазовую корректировку по всему кристаллу. Результат — автомобильный уровень бездефектного качества даже для крупных 3-нм SoC, что критически важно для SDV-платформ с постоянно растущей программной сложностью.

Продвинутое управление питанием: более 90 доменов, снижение IR-просадки на 13%

Энергоэффективность и безопасность неразрывно связаны в высокопроизводительных автомобильных чипах. В новом SoC Renesas реализовала более 90 независимых доменов питания, обеспечивая тонкое управление нагрузкой в диапазоне от нескольких милливатт до десятков ватт в зависимости от активной задачи.

Силовые ключи разделены на кольцевые и строчные структуры. При подаче питания кольцевые ключи подавляют пусковой ток, а строчные выравнивают импеданс домена. Совместно эти методы снижают IR-просадку примерно на 13% по сравнению с традиционными решениями. Для обеспечения функциональной безопасности конфигурация двойного локстепа (DCLS) назначает независимые ключи и контроллеры питания ведущему и проверочному ядрам, что позволяет немедленно обнаружить сбой любого из них.

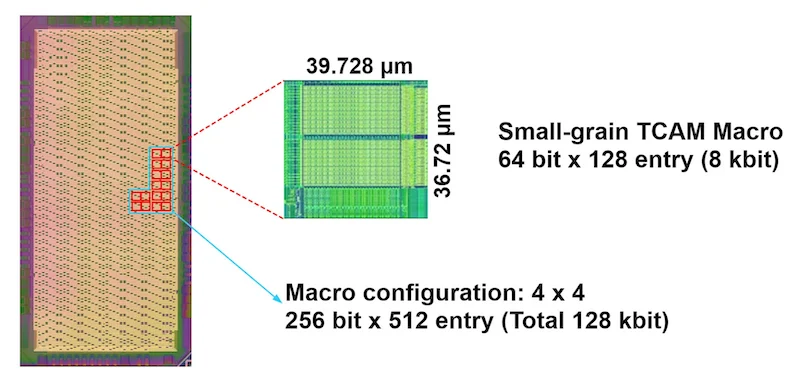

3-нм TCAM: высокая плотность, низкое энергопотребление, функциональная безопасность

Параллельно с работой над SoC для ЭБУ Renesas анонсировала конфигурируемую TCAM на 3-нм техпроцессе FinFET. TCAM обеспечивает параллельные операции поиска, необходимые для маршрутизации, фильтрации и принятия решений в реальном времени — возможности, которые становятся всё важнее по мере того, как автомобили обрабатывают данные от десятков датчиков одновременно.

Архитектура поддерживает гибкую настройку ширины ключа и глубины записей, что позволяет адаптировать её под конкретные автомобильные задачи. В части безопасности Renesas устранила историческое ограничение кода SECDED ECC в TCAM: поскольку ячейки по одному адресу физически соседствуют, двухбитовые программные ошибки традиционно не поддавались исправлению. Renesas решила эту проблему, разнеся чётные и нечётные шины данных для увеличения физического расстояния между пользовательскими данными и битами чётности, превращая потенциальные двухбитовые ошибки в исправляемые однобитовые. Отдельная SRAM для хранения чётности ECC с независимым дешифратором адреса дополнительно улучшает обнаружение записей по неверному адресу.

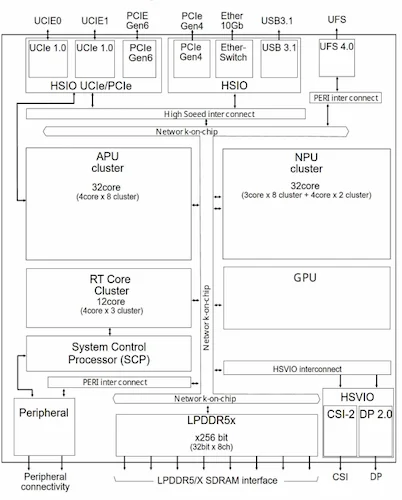

R-Car X5H: всё вместе

Все перечисленные технологии войдут в состав R-Car X5H — флагманского автомобильного SoC пятого поколения Renesas и первого в отрасли мультидоменного автомобильного чипа, произведённого по 3-нм техпроцессу. Устройство способно одновременно выполнять функции систем помощи водителю (ADAS), информационно-развлекательных систем (IVI) и шлюза в рамках единого чипа. Renesas уже начала отгрузку инженерных образцов и отладочных плат вместе с SDK R-Car Open Access (RoX) Whitebox отдельным клиентам и партнёрам, включая Bosch и ZF.

С выходом технологий SoC и 3-нм TCAM на стадию продуктизации Renesas закладывает архитектурный фундамент для централизованных вычислений, гетерогенной чиплетной интеграции и систем памяти, оптимизированных по производительности и соответствию стандарту ISO 26262 в автомобилях следующего десятилетия.